逻辑设计中经常会遇到并行和串行逻辑的概念,并行逻辑通常需要大量的逻辑块输入,如图1所示。采用并行逻辑后,可以减少逻辑的级数,从而改善设计的性能,提高器件工作速度。...在综合工具中,对于这两种逻辑结构的

”逻辑综合“ 的搜索结果

门电路和组合逻辑电路.zip

广东工业大学数字逻辑与EDA设计一、二章综合题

集合与常用逻辑用语综合测试题..docx

高中数学集合逻辑函数向量数列不等式立体几何综合.doc

随着用于逻辑综合,仿真的完全集成的现代计算机辅助设计(CAD)工具的进步,以及诸如现场可编程门阵列(FPGA)的可编程逻辑器件(PLD)中的电路的实现,现在可以非常容易和快速地设计和实现复杂的数字电路。

降低电路功耗,但是其难以被静态时序分析工具分析和计算,且难以生成功能验证向量和自动测试图形向量针对此问题,提出一种组合逻辑环转化方法,以解决硬件描述语言以及高级语言逻辑综合阶段所面临的组合逻辑环拆分...

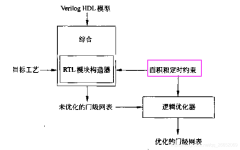

对于我们前端设计工程师来...一般由三步组成:转化(Translation) + 逻辑优化(Logic Optimization) + 映射(Mapping)。 一般先通过read命令将RTL代码转换为通用的布尔(boolean)等式即GTECH格式;然后执行comp...

初学FPGA对综合的理解

标签: FPGA 综合

我对综合理解是: 广义的说综合就是将高层次的设计转化为低层次的...3、逻辑综合:RTL级转化为门级网表 4、结构综合:对门级网表进行布局布线,生成具体的结构。 我们常说的综合是逻辑综合即将RTL级转化为门级网表 ...

2.学习基于该软件平台的数字逻辑电路设计方法; 3.掌握逻辑门的应用及相互转换的方法; 二、实验原理及电路: 1.与非门实现与门 2.与非门实现或门 3.与非门实现或非门 4.与非门实现异或门 5....

会计理论体系逻辑起点的综合评述

从设计角度透视数字集成电路-组合逻辑电路

从设计角度透视数字集成电路-时序逻辑电路

Xilinx 可编程逻辑: 加速推进汽车应用

数字电路和逻辑设计综合实验掷骰子游戏.doc

一、逻辑综合的主要步骤 synthesis = translation + logic optimization + gate mapping DC工作流程主要分为这三步 Translation :主要把描述RTL级的HDL语言,在约束下转换成DC内部的统一用门级描述的电路...

用于大学数字逻辑实验的交通灯控制器

逻辑门电路的识别分类及测量.rar

集合和常用逻辑用语综合测试题(卷).doc

分逻辑函数式的化简、检查、变换3个方面作了详细探讨,且对每个方面给出了相应的见解,即对逻辑函数式的化简方面提出宜采用先卡诺图法再代数法的综合法;对逻辑函数式的检查方面指出了观察互补出现的因子并检验在...

09年综合逻辑真题[参考].pdf

在分析变电站电压无功综合控制问题现状和存在问题的基础上,应用模糊控制理论组成基于模糊逻辑的动态边界电压无功综合控制系统。仿真与实际运行结果表明,该方法能有效地减少变压器分接头和电容器的动作次数,改善控制...

简、逻辑分割、逻辑综合及优化、逻辑布局布线、逻辑仿 真,直至对于特定目标芯片的适配编译、逻辑映射、编程 下载等工作,最终形成集成电子系统或专用集成芯片的一 门新技术,或称为IES/ASIC自动设计技术。

2018届高三数学第5练集合与常用逻辑用语综合练

推荐文章

- 记录nvm use node.js版本失败,出现报错: exit status 1: ��û���㹻��Ȩ��ִ�д˲�����_nvm use失败-程序员宅基地

- lua面向对象编程之点号与冒号的差异详细比较-程序员宅基地

- 百度云虚假下载_虚假新闻:关于公共云的5种常见误解-程序员宅基地

- Tesseract图像识别OCR的学习1_tesseract doocr-程序员宅基地

- 不同层级的Android开发者的不同行为,我们该如何进阶和规划?-程序员宅基地

- Pelee: A real-time object detection system on mobile devices-程序员宅基地

- Hadoop环境搭建(保姆级教学)_hadoop平台搭建步骤-程序员宅基地

- ZooKeeper实战之ZkClient客户端实现负载均衡_zookeeper实现负载均衡案例-程序员宅基地

- Android 枚举 VS 枚举注解_android 枚举注解-程序员宅基地

- HDU1715--第i个斐波那契数 大菲波数_返回第i个斐波那契数-程序员宅基地