”时钟恢复“ 的搜索结果

AD9549采用了一种基于美国模拟器件公司专有的DDS(直接数字合成)技术的新架构设计,可以实现更为稳定的保持(holdover),能有更多的时间来实现故障停机时的时钟基准恢复。如果一路输入基准时钟失效,则时钟发生器IC...

在主电源切断前存储在寄存器中的信息,可在电压恢复后的任何时候读出。 本产品因为内置了时钟校正功能,所以可以在很宽的范围内校正因振荡电路的频率偏差所导致的时钟数据的提前或滞后。通过此功能和温度传感器的...

注意,虽说PCIE时钟有三种架构,但是最常用的还是CC架构,无特殊情况,不要使用其他时钟架构,如果真的要使用其他两种架构,也需要严谨评估先。鉴于PCIE时钟要求多且复杂的,故此文章主要鉴于上一篇文章,给出主要的...

在传输数字信号的时候,需要时钟定时,本程序可以从数据中恢复出时钟

自动或手动触发/恢复 PLL2 集成式低噪声 VCO 50% 占空比输出分离,1 至 1045(偶数和奇数) LVPECL、LVDS 或 LVCMOS 可编程输出 精密数字延迟,固定或动态可调 25 ps 步长模拟延迟控制 2 个差动输出 4 个单端输出 0 ...

本文档将深入介绍内部时钟源模块(Internal Clock Source, ICS),该模块可以在部分HCS08 系列微控制器 中找到。对HCS08 MCU 来说, ICS 模块不但是一个非常 ...式下恢复的特性及内部时钟参考的校准方法。

AD9549采用了一种基于美国模拟器件公司专有的DDS(直接数字合成)技术的新架构设计,可以实现更为稳定的保持(holdover),能让设计者有更多的时间来实现故障停机时的时钟基准恢复。如果一路输入基准时钟失效,则...

主时钟通常是FPGA器件外部的板级时钟(如晶振、数据传输的同步时钟等)或FPGA的高速收发器输出数据的同步恢复时钟信号等。

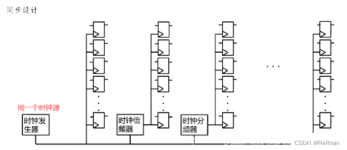

时钟的基础知识 数字设计中,“时钟”表示在寄存器间可靠地传输数据所需的参考时间。Vivado的时序引擎通过时钟特征来计算时序路径需求,通过计算裕量(Slack)的方法报告设计时序空余。时钟必须有合适的定义,包含...

跨时钟域处理 3 大方法揭秘

标签: 跨时钟域

hwclock是Linux系统中的一个重要工具,它主要用于读取和设置硬件时钟。本文将围绕和两个命令进行深入探讨。

虽然SYSCLK有多种时钟源,但一般不用我们管,ST提供的标准库函数已经配置了,选择的时钟源是外部8MHZ晶振经过PLL锁相环9倍频,即SYSCLK默认是72MHZ,然后过AHB分频器,对应寄存器默认为0,即1分频(不分频),即AHB...

CSMF时钟和VSMF压控器件采用LVCMS,LVPECL和LVDS输出格式,使VSMF非常适用于SONET/SDH、吉比特以太网、时钟 /数据恢复和DSL,而CSMF器件还可用在光纤信道。两器件采用5x7mm陶瓷封装,在35~45mA,工作电压为2.5~3.3...

第七章 时钟体系 时钟信号是数字时序电路的“脉搏”,电路每接收到一个周期的时钟信号,就做一个相应的动作。因此,在允许的范围内,时钟信号的快慢直接决定着电路性能的好坏。在片上系统(SOC)中,不同的模块...

整个钟表的工作是在1Hz信号的作用下进行,这样每来一个时钟信号,秒增加1秒,当秒从59秒跳转到00秒时,分钟增加1分,同时当分钟从59分跳转到00分时,小时增加1小时。按动按键开关的S1、S2小时和分钟开始步进,进行...

FPGA设计之门控时钟

标签: 门控时钟

FPGA设计之门控时钟一、什么是门控时钟二、门控时钟降低功耗的原理1. FPGA功耗分类2. 为什么门控时钟可以降低功耗三、不合理的门控时钟设计1.伪门控时钟2.直接门控时钟四、推荐的门控时钟设计1.基于锁存器的门控时钟...

wsl时钟重要说明:这不是官方的解决方案,尽管它在我的计算机上可以正常使用,但这是不受支持的解决方法:-) WSL存在一个问题,当主机从睡眠/Hibernate模式恢复时,WSL中的时钟未更新。 例如此存储库具有一种变通...

虚拟时钟可以暂停和恢复,加速,减速甚至倒退,可以限制为不超过某个最小值或最大值,或者在达到所设置的最小值或最大值时进行循环。 时钟可以注册回调,回调应在特定的时钟时间触发,一次或每次到达指定时间都将...

1588 ACR(1588 Adaptive clock recovery)是基于1588v2的自适应时钟恢复算法,它是通 过在NE等设备与时钟服务器之间以三层单播报文形式建立时钟链路。然后通过1588报 文的交互,实现设备与时钟服务器时钟的同步。

推荐文章

- 《python爬虫练习》之随机的User-Agent请求头_python 随机useragent-程序员宅基地

- 使用Spring Security、Spring Data Jpa实现的RBAC权限控制_rabc jpa-程序员宅基地

- 微信怎么录屏聊天记录?这两个方法值得收藏!-程序员宅基地

- div的定义div的用法 div的属性(最全的div学习页面)_</div>-程序员宅基地

- Spring Boot 入门之消息中间件篇(五)_springbootfrom 'file:/d:/%e5%85%ac%e5%8f%b8%e9%a1%-程序员宅基地

- javascript下载_免费JavaScript下载-程序员宅基地

- mmap内存映射/dev/mem到用户空间 + kernel config_devmem mmap:operation not permitted-程序员宅基地

- 树莓派C++开发机器人智能小车(11)超声波传感器连线和编程_超声波传感器避障算法 c++-程序员宅基地

- adb安装apk程序_adb install 安装apk-程序员宅基地

- 十三个经典算法研究与总结、目录+索引-程序员宅基地