文中基于2.5 GB/s的高速型数据收发器模型,采用SMIC 0.18 μm的双半速率CMOS时钟进行数据的恢复处理。设计CMOS时钟主要包含:提供数据恢复所需等相位间隔参考时钟的1.25 GHz、16相频锁相环电路;采用电流逻辑模式...

”时钟恢复“ 的搜索结果

简称 ADI)推出的ADN2817,ADN2818,ADN2804和ADN2806四款最新IC扩展了光网络应用中时钟和数据恢复(CDR)集成电路(IC)的产品种类。数据通信和电信应用设计工程师为提高系统鲁棒性并且简化互通性问题需要器件增加...

高速串行时钟数据恢复

标签: 数据恢复时钟

随着数字电路从并行发展到高速串行,高速串行时钟数据恢复

差分信号差分传输是一种信号传输的技术,区别于传统的一根信号线一根地线的做法,差分传输在这两根线上都传输信号,这两个信号的振幅相等,相位相反。在这两根线上传输的信号就是差分信号。差分信号又称差模信号,是...

一种用于时钟恢复,自校电路

标签: 时钟恢复

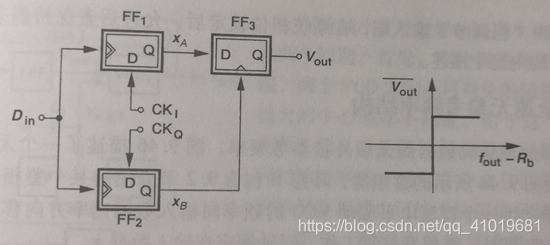

一种用于时钟恢复的电路,本文叙述一种解决这一问题的新方法,电路简单而且自身校正。

本文是基于FPGA实现的高速时钟数据恢复电路实现,介绍了一种利用输出时钟在具有不同相位的时钟信号之间进行切换实现高速时钟恢复电路的方法。利用 Altera公司Quartus软件提供的修改逻辑单元和逻辑块锁定及插入buffer...

MPEG的同步机制及其时序时钟恢复.pdf

时钟数据恢复电路_CDR_专利技术分析_王敏

时钟数据恢复(CDR)电路广泛应用于电信、光收发器、数据存储局域网以及无线产品中,随着对于带宽的要求越来越高,以及分配和占用频谱的增加,因而在设计中,CDR技术的优势将日益突出。与此同时,供应商的产品都将系统...

此压缩文件是对gardner算法利用插值滤波实现定时恢复的matlab仿真。包含了三个文件,一个word文档,对程序作了详尽说明;另一个m文件

本文简要说明眼图相关的知识,参考是德科技的文章。

在有线通信中,需要从数据中恢复时钟。将时钟编码到 数据中的优点是可以省却发送时钟的线路,也有助于处理偏 移问题。 SERDES(串行器-解串器)器件诸如SCAN25100可以 接收一组并行数据并将其转化为一组串行数据,...

pcie refclk

美国模拟器件公司(ADI)推出了ADN2817,ADN2818,ADN2804和ADN2806四款最新IC扩展了光网络应用中时钟和数据恢复(CDR)集成电路(IC)系列。数据通信和电信应用设计工程师为提高系统鲁棒性并且简化互通性问题需要器件增加...

高速SerDes时钟数据恢复电路的研究资料

时钟分频原理 如果cpu是计算机的大脑,电流是计算机的血液,那么时钟则是计算机的心脏,时钟频率决定了处理器运算的快慢,它的每一次“跳动”都驱动着处理器不停的执行命令。不同的是,人的各个部位心率是一样的...

介绍了时钟和数据恢复器件ADN2814的主要性能、内部结构和引脚功能,给出了ADN2814在信号传输中的应用电路,同时介绍了系统中时钟和数据恢复器件的选择方法及应用分析。

基于FPGA的高速时钟数据恢复电路的实现.doc

光 通 信 中 采 用 时 钟 与 数 据 恢 复技术实现 2 个功能 :首先 ,利用本地产生的多相位时钟对数据多次采样,判断数据比特的边沿,并通过 PLL 将时钟边沿与其对齐,从而实现与数据同频率 、同相位时钟的恢复 。...

适用于Serdes的插值型时钟数据恢复电路设计_毛少博

同步数字系列(SDH)指针调整给支路时钟带来了幅度很大的低频抖动,一般的时钟同步恢复方法(如简单的模拟或数字锁相环)已无法将其滤除,为恢复SDH中基群时钟同步,提出了一种新的全数字化方法一一统计预测法。...

行业资料-电子功用-时钟数据恢复电路及其方法

0引言时钟数据恢复电路是高速收发器的核心模块,而高速收发器是通信系统中的关键部分。随着光纤在通信中的应用,信道可以承载的通信速率已经可以达到GHz,从而使得接收端的接收速率成为限制通信速率的主要瓶颈。因此...

首先为什么要使用时钟纠正,是因为CDR恢复的用户时钟user_clk和硬核时钟XCLK虽然频率一样,但是会有略微的不同,正是这样导致内部的FIFO有可能读空和写满,这样就会导致传输错误。与其传输出错误,不如我们就发送一...

该文档是基于FPGA实现的高速时钟数据恢复,对用FPGA实现CDR有很大帮助,希望可以帮到学习这一块的工程师。

推荐文章

- YOLO V8车辆行人识别_yolov8 无法识别路边行人-程序员宅基地

- jpa mysql分页_Spring Boot之JPA分页-程序员宅基地

- win10打印图片中间空白以及选择打印机预览重启_win10更新后打印图片中间空白-程序员宅基地

- 【加密】SHA256加盐加密_sha256随机盐加密-程序员宅基地

- cordys 启动流程_cordys服务重启-程序员宅基地

- net中 DLL、GAC-程序员宅基地

- (一看就会)Visual Studio设置字体大小_visual studio怎么调整字体大小-程序员宅基地

- Linux中如何读写硬盘(或Virtual Disk)上指定物理扇区_dd写入确定扇区-程序员宅基地

- python【力扣LeetCode算法题库】面试题 17.16- 按摩师(DP)_一个有名的讲师,预约一小时为单位,每次预约服务之间要有休息时间,给定一个预约请-程序员宅基地

- 进制的转换技巧_10111100b转换为十进制-程序员宅基地