”数字IC设计学习“ 的搜索结果

看到很多小伙伴都不了解数字IC设计该怎么学,下面就来给大家来具体讲讲。

数字IC入门基础(汇总篇)

标签: 数字IC

数字IC设计学习笔记 STA基本概念 1. STA基本概念 2. 时序弧概念 Timing Arc 3. 建立时间和保持时间概念 4. 时序路径概念Timing Path 5. 时钟域概念clock domains 6. 操作条件概念Operating conditions 1. STA基本...

数字IC设计学习笔记 Formality 形式验证 1. 基本特点 2. Reference Design 和Implementation Design 3. container 4. 读入共享技术库 5. 设置Reference Design 6. 设置Implementation Design 7. 保存及恢复所做的...

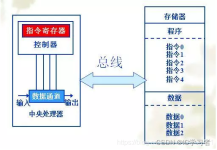

数字IC设计需要学什么?

标签: fpga开发

数字IC设计学习笔记 低功耗设计1 1. 目的 2. 功耗的分析 2.1 功耗的类型 2.2 按结构分类 2.3 反转率的计算 3. 低功耗设计方法 3.1 系统与架构级低功耗设计方法 3.2 RTL级低功耗设计方法 3.3 门级电路低功耗...

数字IC设计学习笔记 PrimeTime 基本概述 1. PrimeTime 基本概述 2. 运行模式 1. PrimeTime 基本概述 PrimeTime,Synopsys公司提出的,针对于复杂的,全芯片的,门级静态时序分析的工具。可集成在逻辑综合和物理综合...

数字IC设计学习笔记 半周期路径Half Cycle Path 1. 伪路径False Paths 2. 如何处理False Paths 1. TCL置换分类 变量置换$: $ 后面为变量名。将置换成它的值。 命令置换[]:[]内是一个独立的tcl语句 反斜杠置换\:...

数字IC设计学习笔记 多周期路径 Multicycle Paths 1. 多周期路径 Multicycle Paths 2. Setup time 检查 3. Hold time 检查 4. 总结 1. 多周期路径 Multicycle Paths 多周期路径Multicycle Paths:在一些特殊情况,...

数字IC设计学习笔记 静态时序分析 1. 时序分析路经 2. 保持时间 2.1 概念 2.2 路径分析 1. 时序分析路经 Timing path类型: ① In2reg:input port 到 时序元件的数据输入端 ② Reg2reg: 时序元件的时钟pin 到 ...

数字IC设计学习笔记 静态时序分析 1. 亚稳态概念 2. 产生原因 3. 解决方法 4. MTBF平均失效时间 1. 时序分析的四条路经 亚稳态:Metastability,触发器无法在某个规定时间内达到一个可确认的状态。当一个触发器处于...

数字IC设计学习笔记 专业书单整理 1. 数字IC验证相关书籍 2. 数字IC设计相关书籍 1. 数字IC验证相关书籍 芯片验证漫游指南 ---- 刘斌 UVM实战 ---- 张强 SystemVerilog验证 测试平台编写指南[中文版] ---- 克里斯....

数字IC设计学习笔记 配置STA环境1 1. STA环境 2. 指定时钟specifying clocks 3. 生成时钟generated clocks 1. STA环境 STA环境,就是给STA指定一个正确的约束。环境应该精确,以便静态时序分析时,能够指出所有设计...

这是基于Python、Shell 脚本、Verilog、C 语言、UVM 方法搭建的一个文件数据自动...UT 模块验证中,不需要通过 UVM 环境和 SV 语言,就能够实现大批数据量的自动对比,这是数字 IC 设计者和脚本设计者的福音~.........

数字IC设计学习笔记 半周期路径Half Cycle Path 1. 伪路径False Paths 2. 如何处理False Paths 1. 伪路径False Paths 在设计中,有些路径是不可能存在的,或者不可能发生的,这种路径称为伪路径,False Paths。 ...

数字ic设计自学ing

标签: 数字ic

数字IC设计学习笔记 多时钟域 Timing分析 (timing cross clock domain) 1. 慢时钟域到快时钟域 2. 快时钟域到慢时钟域 1. 慢时钟域到快时钟域 Launch:对原时钟做了4分频/频率变成4倍,周期减少到1/4 分频电路,...

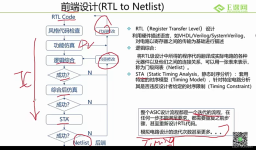

数字逻辑综合工具实践-DC DC多线程 tcl语法 tcl学习 参考资料 DC综合简单总结 DC综合过程和指令 DC/PT 常用到的脚本 某些问题 DC使用时读入多个verilog文件的问题 这里说一下,set list [1 2 3] 不是大括号! if语句...

数字IC设计学习笔记 配置STA环境2 1. 约束 Input path 和 Output path 2. 时序路径组Timing path groups 3. 外部属性建模 1. 约束 Input path 和 Output path 约束 Input path 对于input path的约束,主要针对于...

数字IC设计学习笔记 半周期路径Half Cycle Path 1. 半周期路径Half Cycle Path 2. Setup time 检查 3. Hold time 检查 4. 总结 1. 半周期路径Half Cycle Path 如果在设计中,同时存在上升沿触发的D触发器,以及...

数字IC设计学习笔记 多时钟Timing分析 (Multiple clocks) 1. 多时钟之间是整数倍关系 2. 多时钟之间是非整数倍关系 3. 有相位移动的 1. 多时钟之间是整数倍关系 静态时序分析计算时钟之间公共的周期。前提:只能算...

数字IC设计学习笔记 4. verilog实现BCD计数器 1 原理图 2 Verilog 代码 3 Modelsim仿真 BCD码:Binary-Coded Decimal,二进码十进数,是一种十进制的数字编码,用4位二进制数来表示十进制数中的0~9个十个数之一。...

推荐文章

- Codeforces-学校排队-程序员宅基地

- 计算机毕业设计ssm基于JAVA的图书馆自习室座位预约系统194fd9 (附源码)轻松不求人_基于ssm的图书馆预约座位-程序员宅基地

- 实值复变函数求导 ——(Wirtinger derivatives)_wirtinger导数-程序员宅基地

- VMWare虚拟机设置固定IP上网方法_vm虚拟机只允许指定ip访问-程序员宅基地

- 深度学习修炼(一)线性分类器 | 权值理解、支撑向量机损失、梯度下降算法通俗理解-程序员宅基地

- 基于SpringBoot的社区团购APP+02043(免费领源码)可做计算机毕业设计JAVA、PHP、爬虫、APP、小程序、C#、C++、python、数据可视化、大数据、全套文案-程序员宅基地

- 如何在无公网IP环境下远程访问Serv-U FTP服务器共享文件-程序员宅基地

- uniapp的navigateTo页面跳转参数传递问题_uni.navigateto刷新携带参数丢失-程序员宅基地

- C++中std::getline()函数的用法-程序员宅基地

- vue 工作中的一些小总结(基础知识供刚入门的小伙伴看 vue+elementUi+vsCode+vue-router+iconfont )_mac+elementui+vscode-程序员宅基地