”快表、页表、cache的关系“ 的搜索结果

细致分析TLB Page,Cache 主存 的联系和异同。以及在命中类题型和访存次数类题型中的应用。

教学内容与要求 1掌握处理器在进程地址空间上的三种运行位置,了解内核编程不能使用C库函数和FPU,以及可能产生内存故障、核心栈溢出... 13熟悉页cache和radix_tree,缓冲区cache,和pdflush内核线程原理。(2小时)

我们可以把快表理解为一种特殊的高速缓冲存储器(Cache),其中的内容是页表的一部分或者全部内容。作为页表的 Cache,它的作用与页表相似,但是提高了访问速率。由于采用页表做地址转换,读写内存数据时 CPU 要访问...

2. 相联存储器不按地址而是按A___内容___访问的存储器,在cache中用来存放B___行地址表___,在虚拟存储器中用来存放C___页表快表___。 3. 指令操作码字段表征指令的A___操作特性和功能___,而地址码字段指示B___...

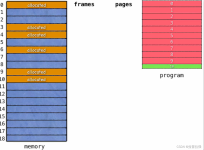

程序运行时 磁盘 主存 Cache TLB 页表的访问关系

多级页表与快表 文章目录多级页表与快表什么是页表页表带来的问题快表多级页表三级页表转换法参考 什么是页表 页表就是一个用于将虚拟地址转换为物理...快表一般存放在 CPU 内部的高速缓冲存储器 Cache。 快表可以直接

分段、分页、页表、快表学习笔记

标签: 学习

目录前言cache高速缓存直接映射全相连映射组相连映射指令缓存与数据缓存虚拟内存(重要⚠)页表缺页替换TLB例题(重要⚠)FastMath 前言 来到存储器章节的复(yu)习。首先引入 cache 高速缓存,来缓解高速的 cpu 和...

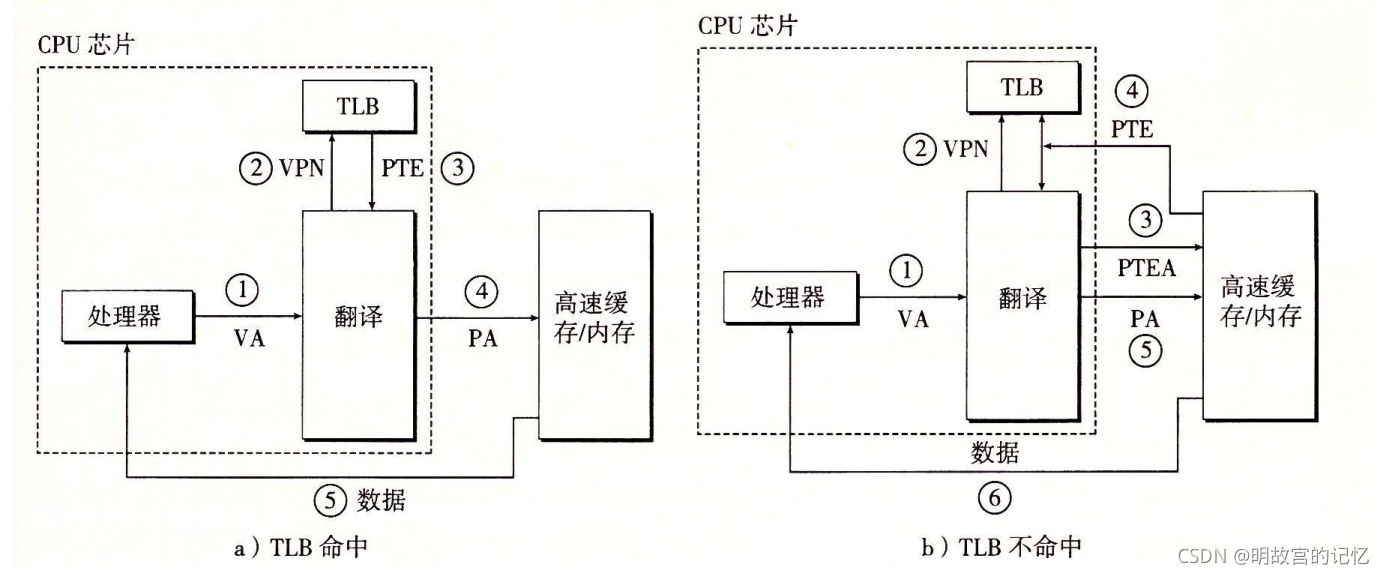

查找顺序从TLB到页表再到Cache和主存的原因是层次化的内存管理结构。 TLB(Translation Lookaside Buffer)是一个高速缓存,用于存储最近使用的虚拟地址和对应的物理地址的映射关系。TLB的目的是加快地址转换的速度...

上一篇博客回顾:计组复习(三):流水化的数据通路,流水线冒险检测与处理在去年的计系 2 课程也讲到了 cache,本篇博客只是简单提一下,详情请戳我之前的博客:计系2复习(4)存储:磁盘存储与cache三种cache映射...

【页表】:特殊数据结构,存放系统空间的页表区域(存放逻辑页与物理页帧的对应关系)。每个进程都有自己的页表,PCB 表中有指针指向页表。(1)逻辑地址(页号,偏移量),逻辑地址就是虚拟地址。(2)物理地址(页...

【计算机组成原理汇总】

标签: 学习

冯诺依曼机 由输入设备、输出设备、运算器、控制器和存储器五大部件构成,以运算器为中心,采用“存储程序”的思想,将指令和数据以同等地位存储在存储器中可按地址寻访。指令由操作码和地址码构成,以二进制形式在...

文章目录块表【1】块表【2】多级页表【3】总结 块表 在页式内存管理中有2个重要的问题: 虚拟地址到物理地址的转换要快 当虚拟空间很大时,相应的...块表作为页表的高速缓存器(Cache),作用与页表的本质作用一致.

理解Cache地址映射之前补充一些基础知识,Cache的地址映射和MMU(内存管理单元)和TLB Cache(转译查找缓存)中的映射是有区别的。Cache、TLB Cache、MMU在CPU中结构如图1所示,图1展现的是Cortex A9 Processor内部...

内存是程序得以运行的重要物质基础。如何在有限的内存空间运行较大的应用程序,曾是困扰人们的一个难题。为解决这个问题,人们设计了许多的方案,其中最成功的当属虚拟内存技术。Linux作为一个以通用为目的的现代...

一)TLB1)TLB的概述TLB是一个内存管理单元用于改进虚拟地址到物理地址转换速度的缓存.TLB是位于内存中的页表的cache,如果没有TLB,则每次取数据都需要两次访问内存,即查页表获得物理地址和取数据.分页与页表概念性...

TLB、页表、Cache、主存之间的访问关系 首先,程序员应该给出一个逻辑地址。通过逻辑地址去查询TLB和页表(一般是同时查询,TLB是页表的子集,所以TLB命中,页表一定命中;但是页表命中,TLB不一定命中),以确定该...

如下页表图表示使用快表(页表)的虚实地址转换条件,快表存放在相联存贮器中,其中容量为8个存贮单元。问: (1)当CPU 按虚拟地址1去访问主存时,主存的实地址码是多少? (2)当CPU 按虚拟地址2去访问主存时,主存的实...

推荐文章

- java实现获取url中的图片保存到本地_java遍历数据库url保存照片-程序员宅基地

- Mac下好用的终端SSH软件:Royal TSX的入门使用指导_royal tsx 可视化界面-程序员宅基地

- Python使用MySQL查询数据导出Excel-程序员宅基地

- 【Word及其他文本工具快捷键大全】_文字工具快捷键-程序员宅基地

- OSG开发笔记(四):OSG不使用osgQt重写类嵌入Qt应用程序_osg开发笔记(四):osg不使用osgqt重写类嵌入qt应用程序-程序员宅基地

- python学习笔记之tkinter中的label_python tkinter labels[i].config(image=none) 无法去除图片-程序员宅基地

- 一阶电路中的时间常数_学电路原理,你得这么做-程序员宅基地

- C语言学生成绩管理系统设计 《C语言程序设计》实训报告_c语言学生成绩管理系统设计报告-程序员宅基地

- 2016年8月6日 星期六 --出埃及记 Exodus 16:6-程序员宅基地

- 软件架构, 软件框架,设计模式的区别_比较架构模式,设计模式,惯用法的区别和联系-程序员宅基地