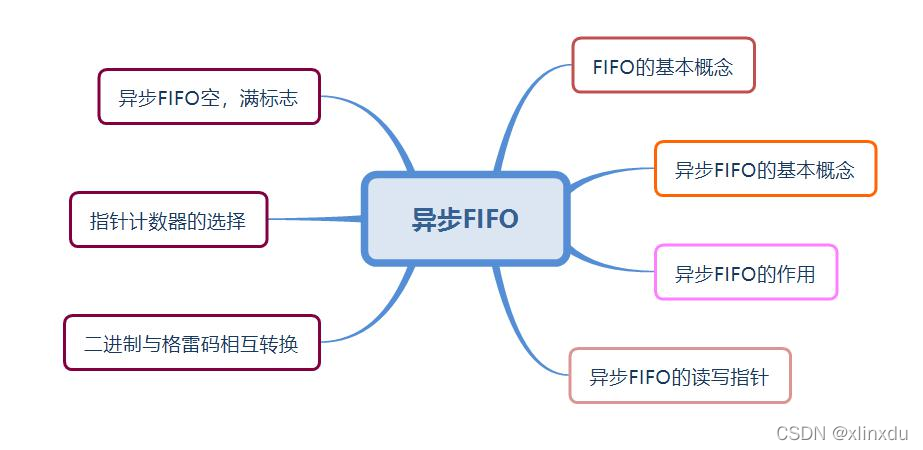

FIFO在硬件上是一种地址依次自增的Single Dul RAM,按读数据和写数据工作的时钟域是否相同分为...本文仅讨论异步FIFO的设计。 因为FIFO的硬件本质是一块Single Dul RAM,无论它的内部结构和原理如何复杂,最核心的...

”异步FIFO设计“ 的搜索结果

摘要:本文介绍如何应用美国QUICKLOGIC公司的QUICKRAM器件设计高速、高可靠异步FIFO(AsynchronousFIFO)。 关键词:异步FIFO 异步FIFO广泛地用于计算机网络工业中进行非同步数据传送,这里的非同步指按一种速率...

本文提出一种新颖的异步FIFO设计方案,它通过先比较读写地址并结合象限检测法产生异步的空/满标志,再把异步的空/满标志同步到相应的时钟域。通过仿真验证,该方法是稳定有效的。

异步FIFO设计思路指导

标签: FIFO

在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以使相异时钟域数据传输的时序...

异步FIFO设计的仿真和综合技术(重点理解).pdf

异步FIFO顾名思义,是写入FIFO中数据的速度和读取FIFO中数据的速度不同,简言之就是写数据的时钟和读数据的时钟不同。异步 FIFO 有两个时钟信号,读和写接口分别采用不同时钟,这两个时钟可能时钟频率不同,也可能...

在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以使相异时钟域数据传输的时序...

FIFO设计错误的方法有很多。FIFO的设计方法有很多, 但 仍然难以对设计进行合理的综合和分析。 本文将详细介绍一种方法, 用于在测试“FIFO满”或“FIFO空”条件之前, 使用同步到不同时钟域的Gray 代码指针来设计,...

异步FIFO设计与使用

标签: afifo

异步FIFO的设计 基本知识 和异步fifo复位以及flush的处理

FPGA内部具有丰富的存储单元,易于实现各种存储器(如FIFO、双口RAM等);另外,基于查找表的逻辑单元可用于实现各种数字信号处理(如滤波等),以辅助DSP处理器做各种预处理。 TI公司推出的高性能数字信号处理芯片...

基于VHDL的异步FIFO设计

标签: FIFO

摘要:FIFO经常应用于从一个时钟域传输数据到另一个异步时钟域...为解决异步FIFO设计过程中空满标志判断难以及FPGA亚稳态的问题,提出一种新颖的设计方案,即利用格雷码计数器(每次时钟到来仅有1位发生改变)表示读/写

本资源包括经典CummingsSNUG2002SJ_FIFO设计文档,以及对应异步fifo verilog rtl实现,以及前仿环境,uvm仿真环境,适合初学者学习fifo原理以及fifo设计。并有相关前仿环境以及uvm环境readme。

双口RAM与异步FIFO设计

标签: 编程语言

本资源是双口 RAM 与异步 FIFO 的设计文件与仿真激励文件,使用 Verilog 语言设计(可综合风格),通过修改 parameter 参数实现不同深度和数据位宽的异步 FIFO。FIFO 读写指针采用格雷码编码,读写指针进行跨时钟域...

无论是数据通讯或者SOC(包括FPGA或者ASIC设计)设计,跨时钟域(clock domain crossing)处理都是一件让人很头疼的事情,无论是在设计的前端或者步入设计的后端,都没有很好的工具去做保证,只能靠设计人员的经验...

推荐文章

- 主线程和子线程的区别_进程主线程子线程-程序员宅基地

- ALBERT文本分类任务实现_albef分类任务-程序员宅基地

- 【好奇心驱动力】ESP32-CAM PIN与GPIO引脚对应关系_esp32cam引脚pin4是哪个gpio-程序员宅基地

- Hive与HBase之间的区别和联系_hive hbase-程序员宅基地

- 【故障诊断】BP神经网络电机数据特征提取与故障诊断【含Matlab源码 2569期】_故障特征量为无编码比值的bp神经网络-程序员宅基地

- BIOS、Legacy BIOS和UEFI BIOS:你需要知道的一切-程序员宅基地

- GitLab集成gitlab-runner_gitlab-runner 16.1.2-程序员宅基地

- 缓存数据库的意义、作用与种类详解-程序员宅基地

- 手把手教你安装VSCode(附带图解步骤)_vscode安装包-程序员宅基地

- Linux下jar包的运行、查看、终止_linux查看jar包是否运行-程序员宅基地