基于双端ram的简单异步fifo设计,输出显示在数码管,empty,full,almost_empty,almost_full输出

”异步FIFO“ 的搜索结果

同步fifo,异步fifo

FIFO的设计,是关于异步的,不错的硬件描述,建议大家好好看看

异步FIFO是一种在电子系统中得到广泛应用的器件,多数情况下它都是以一个独立芯片的方式在系统中应用。本文介绍一种充分利用FPGA内部的RAM资源,在FPGA内部实现异步FIFO模块的设计方法。这种异步FIFO比外部FIFO 芯片...

异步FIFO源代码,由模块调用自动生成,不包含测试向量。

syn_fifo 同步FIFO 模块FPGA设计Verilog源码 quarus工程文件+文档说明,实现异步FIFO读写,且有读写地址产生和保护机制,保护机制,指的是FIFO不能读空和写满。且产生空满信号指示。 module asyn_fifo ( //input ...

基于VHDL的异步FIFO设计

标签: FIFO

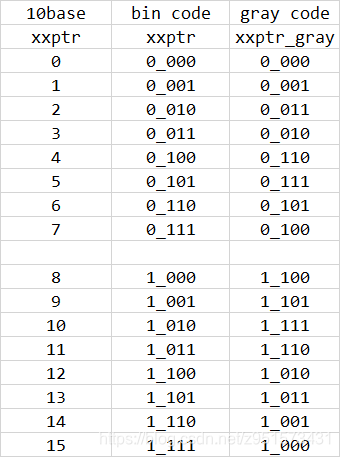

摘要:FIFO经常应用于从一个时钟域传输数据到另一个异步时钟域...为解决异步FIFO设计过程中空满标志判断难以及FPGA亚稳态的问题,提出一种新颖的设计方案,即利用格雷码计数器(每次时钟到来仅有1位发生改变)表示读/写

异步FIFO的verilog代码实现(包含将满和将空逻辑) 异步FIFO简介 异步FIFO关键技术1 -- 读写信号跨时钟域同步 异步FIFO关键技术2 -- 读写地址的比较 异步FIFO关键技术3 -- 将满和将空的产生 FIFO逻辑图 ...

利用异步FIFO实现FPGA与DSP进行数据通信的方案。FPGA在写时钟的控制下将数据写入FIFO,再与DSP进行握手后,DSP通过EMIFA接口将数据读入。文中给出了异步FIFO的实现代码和FPGA与DSP的硬件连接电路。经验证,利用异步...

自己编写的Verilog 异步fifo 有一定的个参考价值 谢谢

verilog 异步FIFO分模块代码 可综合

包括普通同步FIFO和异步FIFO,均为first word fall through模式,同步fifo三种写法,异步fifo三种写法,可参数化配置,接口为fifo的基础接口 提供基础的testbench,两种fifo均在fpga上进行了验证

FIFO(First Input First Output)先入先出队列,这是一种传统的按序执行方法,先进入的指令先完成并引退,跟着才执行第二条指令。FIFO一般用于不同时钟域之间的数据传输。

异步FIFO是一种在电子系统中得到广泛应用的器件,多数情况下它都是以一个独立芯片的方式在系统中应用。本文介绍一种充分利用FPGA内部的RAM资源,在FPGA内部实现异步FIFO模块的设计方法。这种异步FIFO比外部FIFO 芯片...

使用FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法,设计功能正确的FIFO会遇到很多问题,探讨了两种不同的异步FIFO的设计思路。两种思路都能够实现功能正确的FIFO。接下来,详细为你说下“异步fifo为...

高性能异步FIFO

(一)异步FIFO的设计

标签: fpga开发

本文首先对异步 FIFO 设计的重点难点进行分析 最后给出详细代码 一、FIFO简单讲解 FIFO的本质是RAM, 先进先出 ...异步FIFO可以解决跨时钟域的问题,在应用时需根据实际情况考虑好fifo深度即可...

用verilog语言编写并经过综合验证的异步FIFO的源代码

跨时钟域处理,单比特的数据一般采用两级寄存器缓存的方式(适用于由慢到快),多比特则采用异步FIFO、异步双口RAM处理。 二、原理解析 1.空满信号的产生 空信号:读地址赶上写地址时产生空信号,因此同步写地址可以...

格雷码设计异步FIFO,读快写慢,读时钟会出现漏采样的情况,漏采的数据留在FIFO中,导致满信号间断分布。 源文件: module dual_clk_fifo #(parameter DATESIZE = 8, parameter ADDRSIZE = 4, parameter ...

异步FIFO跨时钟域问题,读写时钟不同,不能确定,写满信号和读空信号,采用的FIFO策略是,先写满,写的过程通过帧拉高,帧数据有效等来进入写的状态机,确定写的数量并缓存计数,确定写满。 写满信号到来之后,输出...

推荐文章

- 用好ASP.NET 2.0的URL映射-程序员宅基地

- C语言等级考试是把题目删了,历年全国计算机的等级考试二级C语言上机考试地训练题目库及答案详解(72页)-原创力文档...-程序员宅基地

- Microsoft Office显示正在更新无法打开的问题_正在更新microsoft 365和office-程序员宅基地

- 非常好的Ansible入门教程(超简单)-程序员宅基地

- 【Gradle-8】Gradle插件开发指南-程序员宅基地

- 使用PL/SQL Developer软件解锁_plsqldev表格锁怎么打开-程序员宅基地

- 【Windows Server 2019】Web服务 IIS 配置与管理——配置 IIS 进阶版 Ⅳ_iis默认路径-程序员宅基地

- 网络中的各层协议_发送消息时各层协议-程序员宅基地

- UCRT: VC 2015 Universal CRT, by Microsoft_vc15rt-程序员宅基地

- 关于EntityFramework 7 开发学习_entiry framework 7 书籍-程序员宅基地