一、同步FIFO FIFO表示先进先出的意思。是基于RAM的存储模块,一般多是用于缓冲数据,令模块独立,调用方便、随性。学习FIFO最重要的如何建立先进先出的机制。 图1:先用一个简单的示意图说明: 图1 左边有写入使能...

”异步FIFO“ 的搜索结果

本文首先对异步 FIFO 设计的重点难点进行分析 最后给出详细代码 一、FIFO简单讲解 FIFO的本质是RAM, 先进先出 重要参数: fifo深度(简单来说就是需要存...异步FIFO可以解决跨时钟域的问题,在应用时需根据实际情...

对异步FIFO的全面理解

标签: fifo

什么是异步FIFO? FIFO是一种先进先出的数据缓冲器,与普通的存储器相比,没有外部地址线,其内部地址线自加1,因此FIFO只能顺序写入顺序读出。 异步FIFO的意思就是FIFO的读写时钟是异步的,因此可用于两个不同...

FIFO是英文First In First Out 的缩写,是一种先进先出的数据缓存器,他与普通存储器的区别是没有外部读写地址线,这样使用起来非常简单,但缺点就是只能顺序写入数据,顺序的读出数据, 其数据地址由内部读写指针...

异步FIFO的verilog实现,可以参考一下

异步FIFO功能实现源代码,包含完整的读写指针模块和空满判断模块。

深度为1的异步FIFO设计

标签: fpga开发

深度为1的异步FIFO设计

写时钟100M,每100个写周期写80个数,读时钟80M,每个时钟周期都往外读数据,求异步fifo的最小深度。fifo深度_min =写入数据量 / 写时钟频率 * (写时钟频率 - 读时钟频率);写入速度 = 写时钟频率;

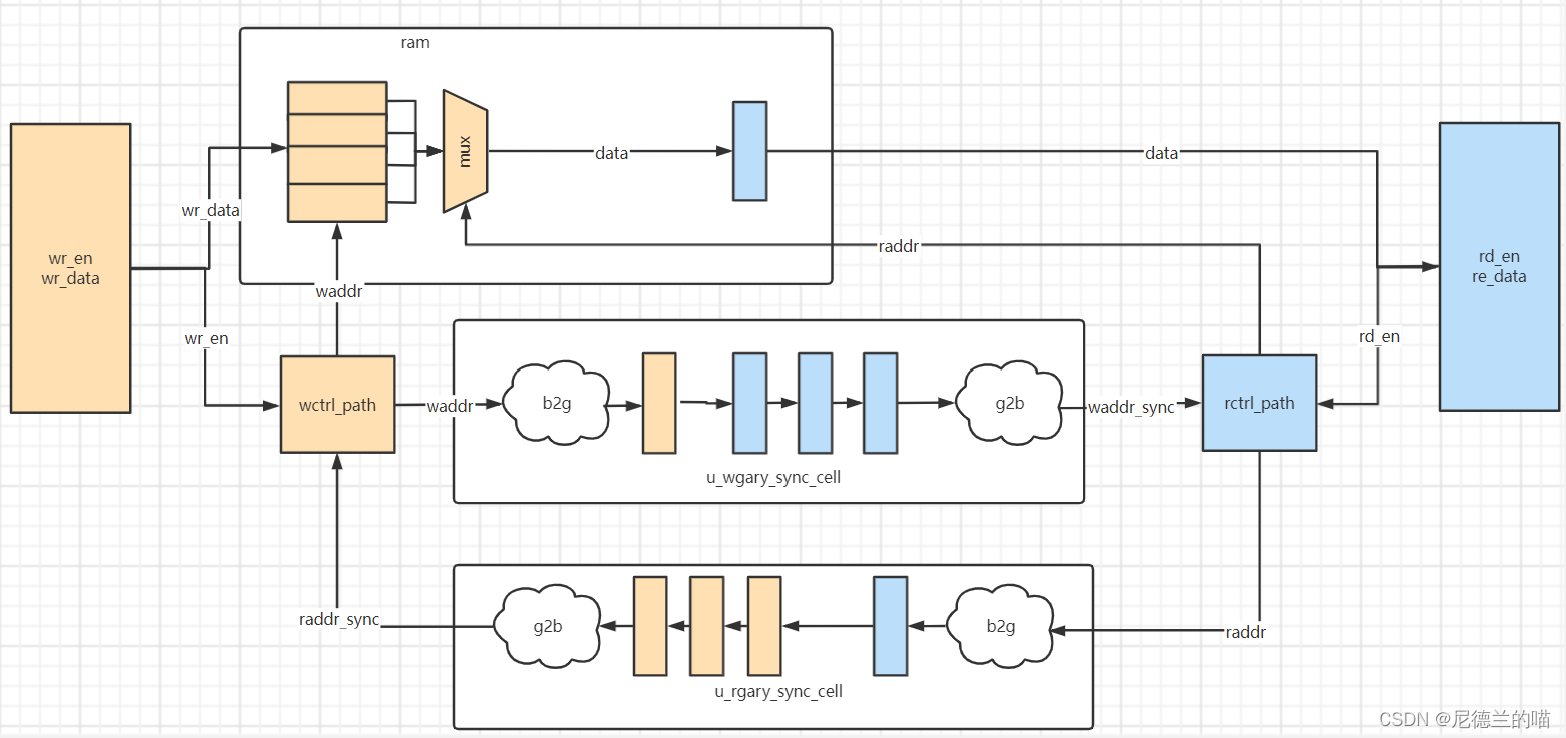

异步FIFO设计一、基本概念二、设计思路2.1 设计前准备工作2.1.1 系统框图2.1.2 格雷码基础2.1.3 异步fifo工作流程举例2.2 RTL建模2.2.1 DPRAM建模2.2.2 WR_LOGIC建模2.2.3 RD_LOGIC建模2.2.4 PIPE模块建模2.2.5 格雷...

在视音频嵌入解嵌系统中,嵌入音频、音频解嵌与音频转换成音频帧标准格式输出都是工作在不同的时钟频率下的。...针对这个问题,本文介绍了一种适合音频解嵌的高效异步FIFO,对通用异步FIFO进行了一些改

异步fifo复位不成功

标签: 学习

记录一下,异步fifo复位不成功,复位信号要在写时钟稳定以后才给,不然fifo会出现异常情况

由于异步FIFO(First In First Out)能够有效解决不同传输速度和不同时钟域之间数据传递的问题,异步FIFO在实际电路中得到广泛的运用。本文介绍一种基于ASIC的高速异步FIFO的设计和实现方案。 1 异步FIFO的基本...

讲解了异步FIFO处理数据时,如何估算FIFO的深度。讲的非常浅显易懂

在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以使相异时钟域数据传输的时序...

异步FIFO时序分析与设计

标签: fpga开发

一、时序分析 1.在读写之前需要将使能信号端拉高; 2.1写时序: 写满信号为0,w_clk上升,将数据写入mem,地址指向下一个位置。 2.2读时序: 读空信号为0,先将当前地址数据读出,后r_clk上升,地址加一,等待下次...

异步FIFO设计与使用

标签: afifo

异步FIFO的设计 基本知识 和异步fifo复位以及flush的处理

异步FIFO(First-In-First-Out,先进先出队列)作为数字系统中的一种基本结构,被广泛应用于设计之中。其可靠性影响整个系统能否正常运行。提出一种折叠式的容错方法,用于提高异步FIFO的可靠性。该方法通过控制逻辑绕...

同步/异步FIFO看这篇就够了~

这个代码主要展示了异步fifo的读的功能和写的功能

异步FIFO的实现,可综合,可验证] keywords:almost_full,full,almost_empty,empty

推荐文章

- lldp中与snmp相关内容agentx-程序员宅基地

- 关闭Mysql的root用户远程访问授权报错Duplicate entry localhost-root for key PRIMARY_error 1062 (23000): duplicate entry 'localhost-roo-程序员宅基地

- LeetCode 818. Race Car-程序员宅基地

- 信息检索笔记-索引构建_为某一文档及集构件词项索引时,可使用哪些索引构建方法-程序员宅基地

- IT巨头英特尔看好中国市场前景-程序员宅基地

- ceph中的radosgw相关总结_radosgw -c-程序员宅基地

- 前端数据可视化ECharts使用指南——制作时间序列数据的可视化曲线_echarts 时间序列-程序员宅基地

- ApplicationEventPublisherAware事件发布-程序员宅基地

- 自定义View实现仿朋友圈的图片查看器,缩放、双击、移动、回弹、下滑退出及动画等_imageview图片边界回弹-程序员宅基地

- PreScan第二课:构建实验_prescan坐标系-程序员宅基地