”异步FIFO“ 的搜索结果

基于verilog的fifo异步实现的源代码和分析。

摘要:使用FIFO同步源自不同时钟域的数据是在数字IC设计中经常使用的方法,设计功能正确的FUFO会遇到很多问题,探讨了两种不同的异步FIFO的设计思路。两种思路都能够实现功能正确的PIFO。 关键词:异步FIFO 握手 ...

FIFO分类,verilog代码实现,最小深度计算

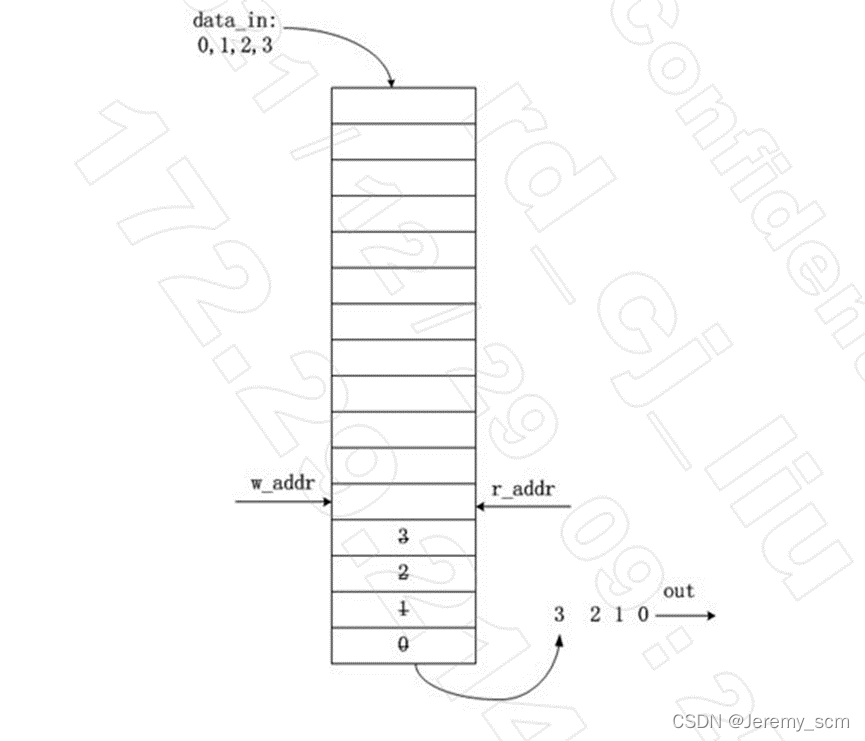

FIFO在硬件上是一种地址依次自增的Single Dul RAM,按读数据和写数据工作的时钟域是否相同分为同步FIFO和异步FIFO,其中同步FIFO是指读时钟和写时钟为同步时钟,常用于数据缓存和数据位宽转换;异步FIFO通常情况下是...

基于verilog的异步fifo设计,仿真效果良好

为什么使用异步FIFO 异步FIFO一般用来解决跨时钟域传输的问题,他的输入和输出对应的时钟不一致,可以理解为蓄水池的问题,一边放水,一边灌水,那么就牵扯到水池的建造规模,也就是深度的计算 异步FIFO深度的计算...

Verilog自编实现异步FIFO,并实现了FWFT、Almost_full与Almost_empty功能

异步FIFO实现 verilog代码,利用格雷码消除亚稳态

在上篇文章同步FIFO中简要介绍了FIFO的基本概念以及同步FIFO的实现。本篇文章将重点介绍异步FIFO的工作原理以及硬件实现。

1、设计异步fifo读写控制,包括读空、写满模块设计,设计可变位宽与深度fifo存储单元。 2、基于UVM搭建验证平台,分别设计读与写agent,设计多个testcase验证设计功能。

该资源是实现了的通过异步fifo进行跨时钟域传输的vivado工程,在不同的时钟域进行fifo数据读写,并用读写地址的格雷码判断fifo空满产生空满标志。工程代码基于vivado2017.4,并在modelsim10.6上仿真成功。工程中附有...

异步FIFO设计思路指导

标签: FIFO

在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以使相异时钟域数据传输的时序...

异步FIFO顾名思义,是写入FIFO中数据的速度和读取FIFO中数据的速度不同,简言之就是写数据的时钟和读数据的时钟不同。异步 FIFO 有两个时钟信号,读和写接口分别采用不同时钟,这两个时钟可能时钟频率不同,也可能...

--rtl 这是源代码 --sim 这是modelsim仿真...已经验证,可以实现异步FIFO 两级寄存器实现读写指针的同步,地址采用格雷码形式防止亚稳态。异步FIFO的源码,个人觉得不易理解,故上传本人最近写的源码,与大家一起分享

本文提出一种新颖的异步FIFO设计方案,它通过先比较读写地址并结合象限检测法产生异步的空/满标志,再把异步的空/满标志同步到相应的时钟域。通过仿真验证,该方法是稳定有效的。

异步FIFO模块验证-面试总结

标签: 面试

IC验证面试之异步FIFO模块验证面试总结

格雷码如果每2^n个数一循环,首尾两个格雷码仍然是只有一位变化,如果不是2^n个数,那么首尾数据就不是仅有一位变化,那就不是真正的格雷码,所以这也是异步FIFO的存储深度只能是2^n的原因。自然二进制码转换成二...

介绍同步FIFO原理,并且提供了verilog源代码;详细介绍了异步FIFO原理和两种实现方法,并提供verilog源代码。

推荐文章

- CentOS 7 安装最新版Docker教程_centos7安装最新版dockers-程序员宅基地

- 敏感字识别算法基于JDK8 lambada表达式_敏感文本识别算法-程序员宅基地

- 华为鸿蒙系统(Huawei HarmonyOS)

- JS读取粘贴板内容-程序员宅基地

- Win10系统下软件UI显示不完整解决方案_用苹果设计的ui在win显示不明显-程序员宅基地

- HTTP方式在线访问Hadoop HDFS上的文件解决方案

- WordPress优化Google广告加载速度_wordpress 怎么做谷歌优化-程序员宅基地

- c# controls.add 控件的使用 ,间接引用还是值引用_this.controls.add-程序员宅基地

- 占位式插件化一Activity的跳转_activity跳转 插件-程序员宅基地

- PTA 剥洋葱(C语言 + 详细注释 + 代码超简单)_c语言pta怎么使用-程序员宅基地