”异步FIFO“ 的搜索结果

摘要:本文介绍如何应用美国QUICKLOGIC公司的QUICKRAM器件设计高速、高可靠异步FIFO(AsynchronousFIFO)。 关键词:异步FIFO 异步FIFO广泛地用于计算机网络工业中进行非同步数据传送,这里的非同步指按一种速率...

思朗科技,2022提前批,数字IC验证,笔试题:异步FIFO的UVM环境搭建及验证。 给了一个异步FIFO的代码工程,要求自己搭建UVM验证环境去验证这个设计,结果包括覆盖率收集以及错误点等等。 适合2023届目标IC验证领域的...

2022提前批,数字IC验证,笔试题:异步FIFO的UVM环境搭建及验证。 给了一个异步FIFO的代码工程,要求自己搭建UVM验证环境去验证这个设计,结果包括覆盖率收集以及错误点等等。 适合2023届目标IC验证领域的小伙伴做一...

set_max_delay [-datapath_only] -from [ node_list] -to [node_list] delay_value

FPGA设计一个读写时钟不同的异步FIFO。

| MSB_FIFO | – | 1(默认值)表示高位先进先出,0表示低位先进先出例如输入4bit,输出8bit,则首先输入的认为是8bit的高4位,接着输入的认为是8bit的低4位。同理,如果输入8bit,输出4bit,则首先输出的会是8bit的...

对异步FIFO的一些简单验证

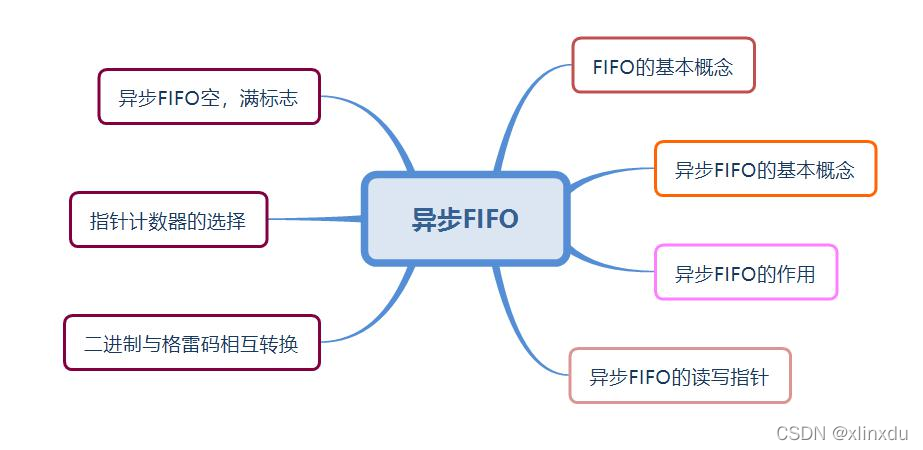

FIFO,即First In First Out ,是一种先进先出的数据缓存器,异步FIFO 是指读写时钟不一致,读写时钟是互相独立的。数据从一个时钟域写入FIFO缓冲区,并从另一个时钟域的同一FIFO缓冲区中读取数据,使用异步FIFO可以...

SV小项目—异步fifo的简单验证环境搭建(全)_Verification_White的博客-程序员宅基地_fifo验证.mht

异步FIFO,Verilog源码实现异步FIFO,异步FIFO的原理,

前面的博文已经讲了异步FIFO和同步FIFO,但并没有实现FIFO的读写位宽转换功能,此功能是FIFO的主要功能之一,应用十分广泛,因此,在前面两个模块的基础上,本文使用纯Verilog实现了读写位宽不同的FIFO,并仿真验证...

写时钟100M,每100个写周期写80个数,读时钟80M,每个时钟周期都往外读数据,求异步fifo的最小深度。fifo深度_min =写入数据量 / 写时钟频率 * (写时钟频率 - 读时钟频率);写入速度 = 写时钟频率;

格雷码具有相邻两个地址只有1bit会反转

同步后的写指针与读指针进行比较,如果它们相等或满足其他预定的条件,就表明FIFO为空,从而产生空逻辑信号。产生空状态信号时,实际FIFO中有数据,相当于提前判断了空状态信号,此时不再进行读FIFO数据操作也是安全...

自己写的一个异步fifo,深度宽度都可自定义,包含binary到gray码,gray码到binary转换,异步时域通信,自定义almost full,almost empty等知识,以verilog写的~

本文通过采用异步FIFO的方式给出了这个问题的一种解决方法,并采用Verilog 硬件描述语言通过前仿真和逻辑综合完成设计。 关键词:异步FIFO;时钟域;Verilog引言当今集成电路设计的主导思想之一就是设计同步化,即对...

通常对异步FIFO的格雷码下约束有两个原因,一个是保证异步FIFO的性能,如果格雷码跨异步的delay太长,FIFO传输数据的效率会下降,另一个是保证多比特格雷码在跨时钟域时不会采错,如果不同bit之间的delay不一致,就...

异步fifo进行跨时钟域数据处理

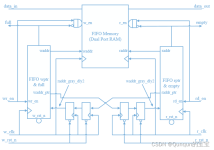

FIFO (先进先出队列)是一种在电子系统得到广泛应用的器件,通常用于数据的缓存和用于容纳异步信号的频率或相位的差异。FIFO的实现通常是利用双口RAM和...1 异步FIFO功能描述 图1给出了FIFO的接口信号和内部模块图

用uvm验证方法学验证异步fifo,文件包括异步FIFOrtl代码和uvm组件

摘要:首先介绍异步FIFO的概念、应用及其结构,然后分析实现异步FIFO的难点问题及其解决办法;在传统设计的基础上提出一种新颖的电路结构并对其进行综合仿真和FPGA实现。 关键词:异步电路 FIFO 亚稳态 格雷码 ...

与ROM或RAM的按地址读写方式不同,FIFO的读写遵循“先进先出”的原则,即数据按顺序写入FIFO,先被写入的数据同样在读取的时候先被读出,所以FIFO存储器没有地址线。FIFO有一个写端口和一个读端口外部无需使用者控制...

在大规模ASIC或FPGA设计中,多时钟系统往往是不可避免的,这样就产生了不同时钟域数据传输的问题,其中一个比较好的解决方案就是使用异步FIFO来作不同时钟域数据传输的缓冲区,这样既可以使相异时钟域数据传输的时序...

面试——异步FIFO详解

标签: 面试

推荐文章

- NSFuzz:TowardsEfficient and State-Aware Network Service Fuzzing-程序员宅基地

- 刘睿民畅谈大数据:政府应紧急设立首席数据官-程序员宅基地

- nginx 编译安装依赖包_nginx编译怎么添加新的依赖库-程序员宅基地

- Python+OpenCV+Tesseract实现OCR字符识别_python + opencv + tesseract-程序员宅基地

- 微型计算机主板上的主要部件,微型计算机主板上安装的主要部件-程序员宅基地

- 推荐一款可匹敌国际大厂的国产企业级低无代码平台_国产私有化 无代码-程序员宅基地

- UE4 蓝图 实现 数组的边遍历边删除_ue4 数组删不掉-程序员宅基地

- python爬虫之bs4解析和xpath解析_from bs4 import beautifulsoup xpath-程序员宅基地

- MySQL配置环境变量-程序员宅基地

- VGG16进行微调,训练mnist数据集_vgg16 tensorflow 2 mnist-程序员宅基地