”zynq“ 的搜索结果

FPGA 、ZYNQ和ZYNQ_Soc

linux3.0 device tree,包括zynq-7000,arm9,coretx-a9芯片级的所有外设驱动树,i2c,spi,dma,中断,gpio

适用于zynq7020的can调试,将库移植和软件移植可以测试can是否正常

ZYNQ 领航者FPGA开发板ZYNQ7020核心板+开发地板PDF原理图+主要器件技术手册,包括: 0-ZYNQ_7010核心板原理图_V1.5.pdf 0-ZYNQ_7020核心板原理图_V1.5.pdf 0-领航者ZYNQ底板原理图_V2.6.pdf AD9708.pdf AMS1117.pdf ...

仿真中有两个比较典型的 一个是Run Behavioral Simulation另一个是Run Post-implementation Timing Simulation,前一个是行为仿真,不存在时序前后的问题,后一个可以查看时序的先后(如输出信号和激励信号之间有...

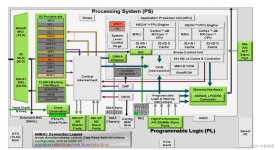

这些外设主要包括 USB 总线接口,以太网接口(ENET),SDI/SDO 接口,I2C 总线接口,CAN 总线接口,UART 接口,GPIO 等。其中BOOT.BIN是由3部分组成的(boot.elf, .bit, fsbl.elf),boot.elf这个是由交叉编译环境产生...

zynq的PL向PS提供时钟和复位,利用蚂蚁T9+控制板开发

本教程提供从vivado平台开始对硬件进行编程,然后倒入SDK进行嵌入式系统编程的全部详细过程,初学者可便利学习ZYNQ嵌入式系统的整体开发流程。并对SDK,vivado等软件的熟悉。

自己总结的ZYNQ程序固化的基本流程,包含从fsbl,等原理部分到具体配置流程的简述

Zynq7000 SoC器件中的复位系统包括由硬件、看门狗定时器、JTAG控制器和软件生成的复位。

PL接收来自PS的时钟信号,这些信号可能经过分频或相位调整,以适应PL内部电路的工作频率和时序要求。同时,PL内部的时钟管理单元可以根据需要生成和调整时钟信号,以确保逻辑电路的稳定运行。

ZYNQ 的全称是 Zynq-7000 All Programmable SoC。Zynq-7000 系列是 Xilinx 公司推出的全可编程片上系统(All Programmable SoC),包含 PS(Processing System,处理器系统)和 PL(Programmable Logic,可编程逻辑...

ZYNQ实现yolov3-tiny算法,有各个模块实现的工程及全套代码,包括下面几个部分yolo_acc,yolo_conv,yolo_max_pool,yolo_upsamp,yolo_yolo这几个模块。

zynq7020芯片手册;ug585-Zynq-7000-TRM,zynq著名手册文档ug585;官网如果太慢,可以这里下载

ZYNQ7010 / 7020_AD9363 / AD9364 / AD9361 <<<<<<< HEAD 基于ZYNQ + AD936X的开源SDR硬件 ======= ac6507f2fe1946b64a4697f9ff1226f25c21065f 基于ZYNQ + AD936X的开源SDR硬件 <<<...

Zynq-7000 CPU时钟编程模型是一种灵活且强大的机制,允许用户根据应用需求精确配置和调整CPU时钟频率。

本文章旨在通过解读ALINX的产品——AXU2CGA/B来对ZYNQ UltraScale+ MPSoC的硬件资源有一个大致了解,完成MPSoC所涉及到的一些硬件基本概念和知识的扫盲。

本文基于zynqmp的ps端pcie2.0 x4接口功能和SSD速度测试,其中pcie2.0x4的接口上连接ssd为nvme接口的ssd盘。本文设计vivado的pcie配置、uboot设备树修改、kernel源码修改以及基于dd命令进行NVMe的ssd读写速度的测试。...

Zynq AXIS:完整的DMA系统 此存储库包含使用Xilinx的Zynq FPGA建立基于DMA的项目所需的所有组件。 首先,有一个称为AXIS的硬件模块,可连接到高性能AXI接口端口。 其次,有一个Linux UIO驱动程序,可将低级AXIS控制...

cmd下输入ipconfig查看PC的ip,要与zynq的ip相匹配。程序中zynq的静态ip地址为192.168.1.10,子网掩码为255.255.255.0(每个字段为8bit数据,所以掩码为11111111_11111111_11111111_00000000,为1时ip相对应的位要...

基于a board support package,选择xlnx_zynq7k BSP,编译工具链选择diab,勾选Enable WDB Target Agent,选择next下一步,VxWorks Image Project Multipage Wizard就配置完成。从the New VxWorks Image Project中,...

Zynq DMA Linux 驱动程序 该 Linux 驱动程序已开发为可在 Xilinx Zynq FPGA 上运行。 它是一个包装驱动程序,用于与低级 Xilinx 驱动程序 (xilinx_axidma.c) 对话,该驱动程序连接到在 Zynq FPGA 的 PL 部分中实现的...

采集外部设备的电压值,用FPGA内部自带的XADC

新建工程 --> 新建block design --> 选择zynq system,配置Ethernet、uart、SD卡。注意,这里不能只配置Ethernet,还要配置uart,不然在SDK新建模板的时候会报错。学习在PS端配置以太网。那么现在来学习一下以太网...

PYNQ已经是我开发PL逻辑不可或缺的工具了,PYNQ极具方便性、灵活性,可以快速验证和测试逻辑设计,也可以利用 Python 的丰富库和工具来处理和分析数据,而不需要使用复杂的测试平台或软件环境。

ZYNQ UltraScale+ MPSoc ZU5EV核心板原理图, Zynq UltraScale+MPSoC是Xilinx推出的第二代多处理SoC系统,它在第一代Zynq-7000的基础上进行了全面升级。 该芯片基于业内最先进的16nm FinFET+工艺制程打造,整合了64...

使用zynq 7020 的9371 sdk配置文件

推荐文章

- Response使用 application/octet-stream 响应到前端_application/octet-stream;charset=utf-8-程序员宅基地

- 利用MultipartFile实现文件上传_实现了multipartfile file上传文件时要选择一个栏目,传给后端一个栏目id,如何实现-程序员宅基地

- muduo之Singleton_muduo singleton-程序员宅基地

- html5 动态存储 localStorage.name 和localStorage.setItem()的差别_localstorage.setitem('aa')和localstorage.aa一样吗-程序员宅基地

- 02.loadrunner之http接口脚本编写_http脚本-程序员宅基地

- The server time zone value ‘�й���ʱ��‘ is unrecognized or represents more than one time zone.-程序员宅基地

- 如何打造企业短视频账号的人设?_做的比较有人格化的公司短视频账号-程序员宅基地

- 一个会做饭的程序员如何每天给女朋友带不同的便当?-程序员宅基地

- PendingIntent重定向:一种针对安卓系统和流行App的通用提权方法——BlackHat EU 2021议题详解 (下)_getrunningservicecontrolpanel-程序员宅基地

- python 之 面向对象(反射、__str__、__del__)-程序员宅基地