”PCIe扫盲“ 的搜索结果

前面的文章简单的介绍了一些关于PCIe总线事务层(Transaction Layer)和数据链路层(Data Link Layer)的一些基本概念。这篇文章来继续聊一聊PCIe总线的最底层——物理层(Physical Layer)。在PCIe Spec中,物理层...

自2019年下半年,PCIeGen5正式发布以来,其单个Lane/Channel速率已达32Gbps,传统的FR4电路板支持这么高的速率是完全不可能的事情。即使面对的是Gen4带来的16Gbps,FR4仍在瑟瑟发抖…… 在6GT/s以下的串行通信协议...

某些特殊的应用场合可能要求PCIe设备能够以高可靠性持续不间断运行,为此,PCIe总线采用热插拔(Hot Plug)和热切换(Hot Swap)技术,来实现不关闭系统电源的情况下更换PCIe卡设备。 注:热切换(Hot Swap)和热...

PCIE(Peripheral Component Interconnect Express)是一种计算机扩展总线标准,用于连接外部设备与计算机主板之间的数据传输。PCIe连接的设备可以是显卡、声卡、网卡等。 Flow control(流量控制)是PCIE中的一种...

本文将简要介绍如何使用Jungo公司的WinDriver工具快速开发PCI Express设备驱动,以及相关注意事项。本文所使用的的测试平台信息如下: ※操作系统:Win7 SP1 64bit ... ※PCIe参考设计:ThroughPut Gen

前面的文章中介绍过,为了保证视频、音频等数据得到优先传输,PCIe总线实现了一种叫做Quality of Service(QoS)的机制。QoS可以满足视频、音频等对Latency和实时性(Isochronous)要求比较高(一般不可以被打断)的...

前面的文章中介绍过,每一个PCIe设备可以只有一个功能(Function),即Fun0。也可以拥有最多8个功能,即多功能设备(Multi-Fun)。不管这个PCIe设备拥有多少个功能,其每一个功能都有一个唯一独立的配置空间...

前面的文章提到过PCIe总线(Gen1&Gen2)采用了8b/10b编码,因此其有效数据速率为物理线路上的速率的80%。即Gen1的有效速率为2.0Gbps=2.5Gbps*80%,而Gen2的有效速率为4Gbps=5Gbps*80%。 如果以数据包的Data ...

PCI-Express是继ISA和PCI总线之后的第三代I/O总线,即3GIO。 由Intel在2001年的IDF上提出,由PCI-SIG(PCI特殊兴趣组织)认证发布后才改名为“PCI-Express”。它的主要优势就是数据传输速率高,另外还有抗干扰能力强...

PCIe总线定义的与功耗管理功能(Power Management,PM)相关的主要有:PCI-Compatible PM、Native PCIe Extensions、Bandwith Management和Event Timing Optimization。 其中,PCI-Compatible PM是一种在软件上和...

本文为PCIe扫盲系列博文连载目录篇(第一阶段),所谓第一阶段就是说后面还有第二阶段和第三阶段……第一阶段主要是介绍PCIe总线的发展历史与展望,PCI总线和PCI-X总线的简要回顾,PCIe总线的体系结构入门,PCIe总线...

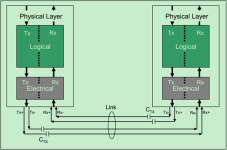

和很多的串行传输协议一样,一个完整的PCIe体系结构包括应用层、事务层(Transaction Layer)...其中,应用层并不是PCIe Spec所规定的内容,完全由用户根据自己的需求进行设计,另外三层都是PCIe Spec明确规范的

PCIe中的Message主要是为了替代PCI中采用边带信号,这些边带信号的主要功能是中断,错误报告和电源管理等。所有的Message请求采用的都是4DW的TLP Header,但是并不是所有的空间都被利用上了,例如有的Message就没有...

前面的文章介绍过PCIe的Gen1和Gen2模式下,物理层使用的是8b/10b的编码。这种编码方式能够实现直流均衡,并且能将数据流中的连0连1控制在5个以内(最多5个连续的1或者0),从而可以降低物理层CDR设计的复杂度。但是8b/...

事务层包(TLP)的一般格式如下图所示: 前面的文章介绍过,TLP Header为3DW或者4DW,Data Payload为1-1024DW,最后的TLP Digest(ECRC)是可选的,为1DW。 TLP Header在整个TLP的位置如下图所示,...

原标题:【博文连载】PCIe扫盲——Ack/Nak 机制详解(一)前面在数据链路层入门的文章中简单地提到过Ack/Nak机制的原理和作用,接下来的几篇文章中将对Ack/Nak机制进行详细地介绍。Ack/Nak是一种由硬件实现的,完全...

一个简单的PCI总线INTx中断实现流程,如下图所示。 1. 首先,PCI设备通过INTx边带信号产生中断请求,经过中断控制器(Interrupt Controller,PIC)后,转换为INTR信号,并直接发送至...

PCIe物理层接口(Physical Interface for PCI Express,PIPE)定义了物理层中的,媒介层(Media Access Layer,MAC)和物理编码子层(Physical Coding Sub-layer,PCS)之间的统一接口,旨在为提供一种统一的行业...

PCIe总线中的链路初始化与训练(Link Initialization & Training)是一种完全由硬件实现的功能,处于PCIe体系结构中的物理层。整个过程由链路训练状态机(Link Training and Status State Machine,LTSSM)自动...

为了保证这些特殊应用的数据包能够得到优先发送,PCIe Spec中为每一个包都分配了一个优先级,通过TLP的Header中的3位(即TC,Traffic Class)。如下图所示: TC值越大,表示优先级越高,对应的包也就会得到优先...

前面的文章介绍过PCIe的Gen1和Gen2模式下,物理层使用的是8b/10b的编码。这种编码方式能够实现直流均衡,并且能将数据流中的连0连1控制在5个以内(最多5个连续的1或者0),从而可以降低物理层CDR设计的复杂度。但是...

PCIe总线自V2.0加入了功能层复位(Function Level Reset,FLR)的功能。该功能主要针对的是支持多个功能的PCIe设备(Multi-Fun PCIe Device),可以实现只对特定的Function复位,而其他的Function不受影响。当然,该...

地址路由(Address Routing)的地址包括IO和Memory。对于Memory请求来说,32bit的地址使用3DW的Header,64bit的地址使用4DW的Header。...注:再次强调,IO请求是为了兼容早期的PCI设备的,在新的PCIe

PCIe总线采用Flow Control的目的是,保证发送端的PCIe设备永远不会发送接收端的PCIe设备不能接收的TLP(事务层包)。也就是说,发送端在发送前可以通过Flow Control机制知道接收端能否接收即将发送的TLP。 在PCI...

PCI-X总线在PCI总线的基础上发展而来,其在软件和硬件层面上都是兼容PCI总线的,但是却显著的提高了总线的性能。也就是说PCI-X的设备可以直接插到PCI的插槽中去,PCI的设备也可以直接插到PCI-X的插槽中去。...

前面的文章中提到过,Ordered Sets分别有以下几种:TS1 and TS2 Ordered Set (TS1OS/TS2OS)、Electrical Idle Ordered Set (EIOS)、FTS Ordered Set (FTSOS)、SKP Ordered Set (SOS)和Electrical Idle Exit Ordered ...

前面的文章提到过高级错误报告(Advanced Error ...在已有的PCIe错误报告机制上(之前文章介绍的),AER还支持以下特性: · 在登记实际发生的错误类型时

之所以把物理层电气部分的文章放在链路初始化与训练文章的后面,是因为这一部分涉及到一些相关的概念,如Beacon Signal、LTSSM等等。 前面已经多次提及,由于本次连载的文章主要是基于Gen2的,所以关于Gen3的...

上一篇文章介绍了Type0型配置空间Header中的BAR的作用和用法,但是PCIe中的桥设备(Switch和Root中的P2P)又是如何判断某一请求(Request)是否属于自己或者自己的分支下的设备的呢?这实际上是通过Type1型配置空间...