”FPGA数据采样“ 的搜索结果

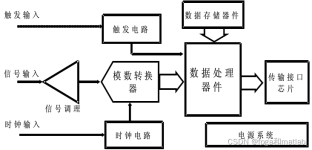

本文介绍了等效时间采样的基本原理、系统实现的具体方案。等效时间采样技术实现了利用低速的ADC器件对宽带模拟信号的采集,降低了系统对ADC器件的要求以及系统实现的复杂度。

信号生成 使用TLV5618 型 DAC 芯片输出正弦波电压 1.DAC驱动

fpga开发,峰值采样计数,verilog代码

FPGA简单实现数据过采样

标签: fpga

FPGA采样AD9238数据并通过VGA波形显示例程 Verilog逻辑源码Quartus工程文件+文档说明,FPGA型号Cyclone4E系列中的EP4CE6F17C8,Quartus版本17.1。 ADC 模块型号为 AN9238,最大采样率 65Mhz,精度为 12 位。实验中把 ...

在现代电子测量、通讯系统以及生物医学等领域,经常涉及对宽带模拟信号进行数据采集和存储,以便计算机进一步进行数据处理。为了对高速模拟信号进行不失真采集,根据奈奎斯特定理, 采样频率必须为信号频率的2 倍...

基于FPGA数据采集系统的设计.pdf

基于FPGA的多通道高精度AD采样系统设计

从概念上讲,对数据向量进行M倍上采样的简单方法是用实际频率分量数的(M-1)倍个零填充数据向量的离散傅里叶变换(DFT)[1],然后将零填充向量转换回时域[1,2]。但这种方法计算量很大,因此不能在FPGA内部高效

本实验练习使用 ADC,实验中使用的 ADC 模块型号为 AN706,最大采样率 200Khz,精度为 16 位。实验中把 AN706 的 2 路输入以波形方式在 VGA 上显示出来,我们可以用更加直观的方式 观察波形,是一个数字示波器雏形

过采样同步数据恢复

基于FPGA的数据遗弃式双口RAM的设计及其在数据采样中的应用.pdf

数据采集在工业测控领域里有广泛的应用,它已成为计算机测控系统的一个重要的环节,尤其在设备故障监测系统中,由于各种设备的结构复杂,运动形式多种多样,发生故障的可能部位很难确定,因此我们需要从设备的各个...

系统由前端模拟电路、采样阵列、多相时钟电路模块、基于FPGA的数据缓冲与修正处理模块构成。系统采样输出数据通过上传到上位机进行显示与性能指标分析。测试结果表明,该TIADC系统通过对失配误差的数字后端补偿后能...

就需要提高采样时钟的频率,但是由于系统的ADC 器件时钟速率并不能达到要求的高频速率或者存储处理速度等不能满足要求因此我们可以采用低速ADC 器件通过等效时间采样来对宽带模拟信号进行数据采集从而使系统易于实现...

就需要提高采样时钟的频率,但是由于系统的ADC 器件时钟速率并不能达到要求的高频速率或者存储处理速度等不能满足要求因此我们可以采用低速ADC 器件通过等效时间采样来对宽带模拟信号进行数据采集从而使系统易于实现...

基于FPGA的低功耗等效数据采样装置.pdf

ADC高速采样基于时间交替采样结构实现,以FPGA为逻辑控制芯片,DSP为误差矫正算法处理中心。在对系统总体设计各模块进行介绍的基础上,重点分析了系统存在的偏移误差、时延误差和增益误差,并描述了一种误差矫正方法...

FPGA使用ISERDES2过采样

标签: 过采样

针对高速并行ADC时间交叉采样技术对多相时钟信号的高要求以及采集数据的误差,介绍了多相时钟设计的一种方法和利用FFT技术实现对增益误差的校正。通过实验仿真证明,该设计能够有效提升数据采集系统的性能。

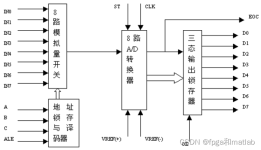

本论文介绍了基于FPGA的多通道采样系统的设计。用FPGA设计一个多通道采样控制器,利用VHDL语言设计有限状态机来实现对AD7892的控制。由于FPGA器件的特性是可以实现高速工作,为此模拟信号选用音频信号。由于...

如下图所示一个场景,FPGA系统工作时钟是125M,此时所能容忍的单片机与FPGA接口的SPI工作时钟最快是多少,本案例只考虑异步采样,后续有机会补充使用spi_clk采样的情况。

关于在FPGA存储AD采样值 利用何种截位方式可以避免带来直流分量给出matlab仿真,并说明原因.zip

推荐文章

- ipad的正确使用方法视频,ipad的正确使用方法图解_ipad9右边两个键是什么-程序员宅基地

- Wireshark数据抓包分析——网络协议篇-程序员宅基地

- GPS系统跟踪捕获算法的Verilog实现_gps的ca码设计与相关verilog程序-程序员宅基地

- 苹果 macOS Sonoma 14 开发者预览版 Beta 3 发布_mac os sonoma最新版本-程序员宅基地

- ES6-17【类、类的继承、类的实现、类的修饰】_es6 类修饰 详解-程序员宅基地

- Java 常用类 03 可变字符串和BigDecimal(BigInteger)_java字符串和bigdecimal类-程序员宅基地

- 【基于FPGA的芯片设计】32×32位寄存器堆_fpga2s需要多少位寄存器-程序员宅基地

- STM32F103 软件实现随机数_stm32f103c8t6可以生成随机数么-程序员宅基地

- 微信h5页面打开微信内置地图及wx.openLocation回调成功调不起页面的问题_h5 wx.openlocation-程序员宅基地

- Linux——部署DNS服务二: 正向解析,反向解析,双向解析_用于减少域名到ip地址的映射的技术是-程序员宅基地