【FPGA】串口通信UART_uart串口通信在发送模块和接收模块加fifo-程序员宅基地

文章目录

一、UART串口通信

一、基本概念

串口是串行接口(serial port)的简称,也称为串行通信接口或COM接口。

串口通信是指采用串行通信协议(serial communication)在一条信号线上将数据一个比特一个比特地逐位进行传输的通信模式。

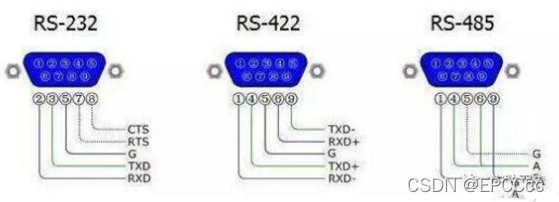

串口按电气标准及协议来划分,包括RS-232-C、RS-422、RS485等。

二、串口数据

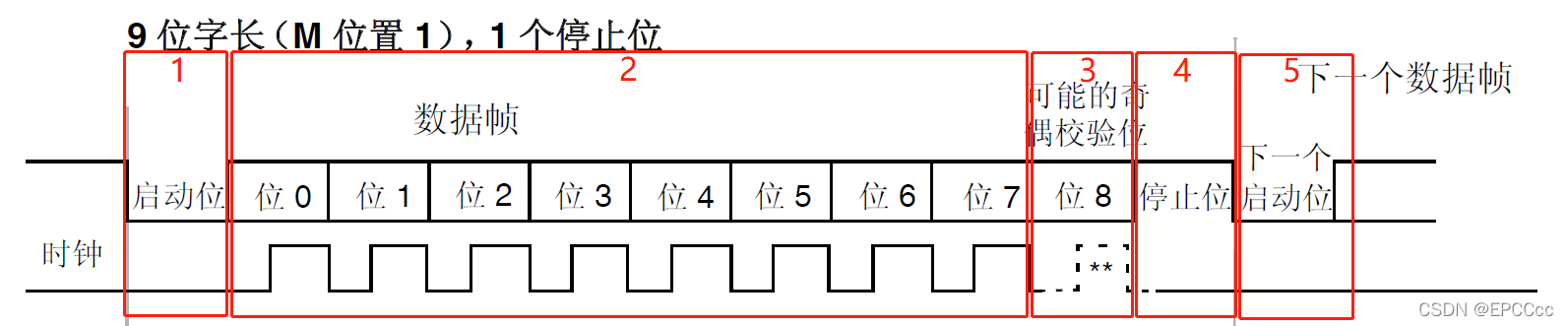

- 起始位:0

- 数据位:可以是6/7/8位数据

- 奇偶校验位(可有可无):奇偶校验就是相对于数据里的1来说,如果是奇校验,有奇数个1就是在奇偶校验位是0,否则奇偶校验位是1,如果是偶校验,有奇数个1就是在奇偶校验位是1,否则奇偶校验位是0,总的来说,奇校验就是看数据位里的加上奇偶校验位(一共9位)是否是奇数,偶校验反之。

- 结束位:1

三、了解波特率

波特率表示每秒钟传送的码元符号的个数,是衡量数据传送速率的指标。

我们常常使用的是RS-232-C,RS-232-C标准规定的数据传输速率为50、75、100、150、300、600、1200、2400、4800、9600、19200、38400波特。

二、串口UART思路设计

其实串口算是一个较简单的协议了,不需要有状态机,只需要有2个计数器就可以搞定,1个是波特率计数器,用来何时收发数据,1个是bit计数,顾名思义记串口的数据bit的,串口分为2个模块,1个是接收模块,1个是发送模块

- 接收模块

在波特率中间稳定的时候去采集数据,第一位为起始位,是0,所以检测到下降沿,给一个标志就可以采集数据位了,最后串并转换。 - 发送模块

从上位机发来的数据,然后最后串并转换的时候在头部加上起始位,在尾部加上结束位即可。

三 、代码部分

这部分我自己写的,如果有问题,请及时通知我。

代码注解比较详细吧。

一、串口接收模块

// 串口接收模块

module uart_rx(

input clk,

input rst_n,

input baud_sel,// 波特率的选择

input din,// 串口接收模块接收到主机来的1bit的数据

output [7:0] dout,// 串口接收模块串并转换的数据发送

output dout_vld

);

parameter SCLK = 50_000_000;// 50MHZ系统时钟

localparam BAUD_9600 = SCLK/9600,// 9600HZ波特率周期

BAUD_115200 = SCLK/115200;// 115200HZ波特率周期

// 波特率计数器

reg [12:0] cnt_baud;

wire add_cnt_baud;

wire end_cnt_baud;

reg [12:0] baud;

// bit计数器

reg [3:0] cnt_bit;

wire add_cnt_bit;

wire end_cnt_bit;

// 对输入的1bit数据打拍

// 因为开始位是0,,停止位是1

reg din_r0;

reg din_r1;

// 检测到下降沿开始输入接收

wire din_nedge;

// 检测到下降沿的标志

reg din_nedge_flag;

// 寄存串并转换的接收到的数据9位开始位+停止位+数据8位

reg [9:0] rx_data;

reg rx_data_vld;

// 波特率计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_baud <= 0;

end

else if(add_cnt_baud)begin

if(end_cnt_baud)begin

cnt_baud <= 0;

end

else begin

cnt_baud <= cnt_baud + 1;

end

end

else begin

cnt_baud <= cnt_baud;

end

end

assign add_cnt_baud = din_nedge_flag;

assign end_cnt_baud = add_cnt_baud && cnt_baud == baud - 1;

// bit计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_bit <= 0;

end

else if(add_cnt_bit)begin

if(end_cnt_bit)begin

cnt_bit <= 0;

end

else begin

cnt_bit <= cnt_bit + 1;

end

end

else begin

cnt_bit <= cnt_bit;

end

end

assign add_cnt_bit = end_cnt_baud;

assign end_cnt_bit = add_cnt_bit && cnt_bit == 10 - 1;

// 波特率的选择9600 115200

always @(*)begin

case(baud_sel)

0 : baud = BAUD_9600;

1 : baud = BAUD_115200;

default : baud = BAUD_9600;

endcase

end

// 同步打拍

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

din_r0 <= 0;

din_r1 <= 0;

end

else begin

din_r0 <= din;

din_r1 <= din_r0;

end

end

// 下降沿检测

assign din_nedge = ~din_r0 & din_r1;

// 下降沿检测标志

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

din_nedge_flag <= 0;

end

else if(din_nedge)begin

din_nedge_flag <= 1'b1;

end

else if(end_cnt_bit)begin

din_nedge_flag <= 1'b0;

end

end

// 在波特率中间取稳定的值

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rx_data <= 0;

end

else if(add_cnt_baud && cnt_baud == (baud >> 1) - 1)begin

rx_data[cnt_bit] <= din;

end

end

assign dout = rx_data[8:1];

// 数据有效

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rx_data_vld <= 0;

end

else if(end_cnt_bit)begin

rx_data_vld <= 1;

end

else begin

rx_data_vld <= 1'b0;

end

end

assign dout_vld = rx_data_vld;

endmodule

二、串口发送模块

module uart_tx(

input clk,

input rst_n,

input baud_sel,// 波特率的选择

input [7:0] din,// 串并转换的数据

input din_vld,// 串并转换的数据有效

output dout,// 发送模块发送的1bit数据

output busy // 发送模块忙标志

);

parameter SCLK = 50_000_000;// 50MHZ系统时钟

localparam BAUD_9600 = SCLK/9600,// 9600HZ波特率周期

BAUD_115200 = SCLK/115200;// 115200HZ波特率周期

// 波特率计数器

reg [12:0] cnt_baud;

wire add_cnt_baud;

wire end_cnt_baud;

reg [12:0] baud;

// bit计数器

reg [3:0] cnt_bit;

wire add_cnt_bit;

wire end_cnt_bit;

// 寄存发送模块接收的数据有效

reg rx_data_vld_flag;

// 寄存要发送的数据

reg [9:0] tx_data;

// 波特率计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_baud <= 0;

end

else if(add_cnt_baud)begin

if(end_cnt_baud)begin

cnt_baud <= 0;

end

else begin

cnt_baud <= cnt_baud + 1;

end

end

else begin

cnt_baud <= cnt_baud;

end

end

assign add_cnt_baud = rx_data_vld_flag;

assign end_cnt_baud = add_cnt_baud && cnt_baud == baud - 1;

// bit计数器

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

cnt_bit <= 0;

end

else if(add_cnt_bit)begin

if(end_cnt_bit)begin

cnt_bit <= 0;

end

else begin

cnt_bit <= cnt_bit + 1;

end

end

else begin

cnt_bit <= cnt_bit;

end

end

assign add_cnt_bit = end_cnt_baud;

assign end_cnt_bit = add_cnt_bit && cnt_bit == 10 - 1;

// 波特率的选择9600 115200

always @(*)begin

case(baud_sel)

0 : baud = BAUD_9600;

1 : baud = BAUD_115200;

default : baud = BAUD_9600;

endcase

end

// 数据有效的标志

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

rx_data_vld_flag <= 0;

end

else if(din_vld)begin

rx_data_vld_flag <= 1'b1;

end

else if(end_cnt_bit)begin

rx_data_vld_flag <= 1'b0;

end

end

// 数据有效添加开始位和停止位

always @(posedge clk or negedge rst_n)begin

if(!rst_n)begin

tx_data <= 0;

end

else if(din_vld)begin

tx_data <= {1'b1,din,1'b0};

end

end

// 数据有效标志1bit数据发送,之后都发高位,不能发低位

assign dout = rx_data_vld_flag?tx_data[cnt_bit]:1'b1;

// 这个busy有待商榷

assign busy = rx_data_vld_flag;

endmodule

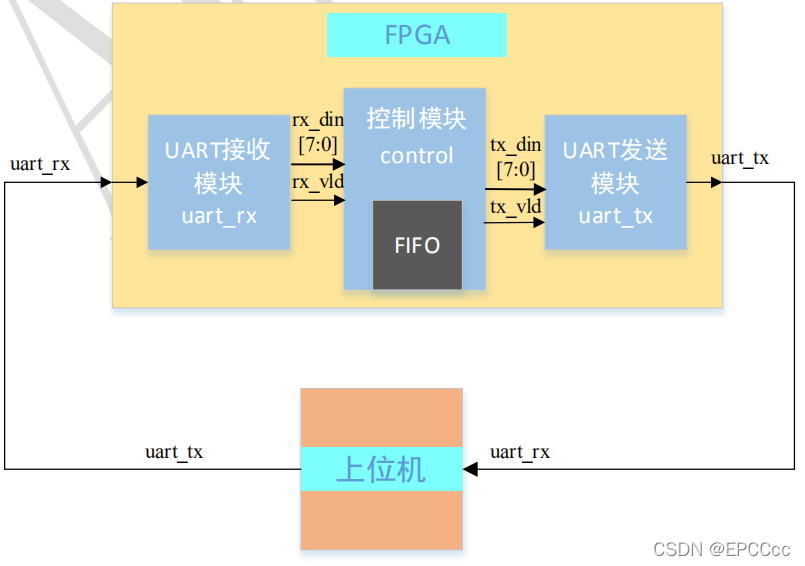

四、串口回环实验

任务要求

FPGA 与上位机通过串口通信,完成数据环回;

波特率可调,即可以选择 115200、57600、38400 等;

使用 FIFO 作为数据缓存单元

系统框图

难的不是串口接收发送模块,难的是串口控制的fifo,对于fifo的使用我还不太熟悉,fifo的读写请求和数据要一致,还有fifo的前显模式和正常模式。

串口控制模块

// 串口控制模块

module uart_ctrl(

input clk,

input rst_n,

input [7:0] din,// 接收模块8位数据

input din_vld,// 接收模块8位数据的

input busy,

output [7:0] dout,

output dout_vld

);

wire rdreq;

wire wrreq;

wire empty;

wire full ;

wire [7:0] q_out;

wire [4:0] usedw;

// 用fifo缓存数据,来控制读写

fifo fifo_inst (

.aclr ( ~rst_n ),

.clock ( clk ),

.data ( din ),

.rdreq ( rdreq ),

.wrreq ( wrreq ),

.empty ( empty ),

.full ( full ),

.q ( q_out ),

.usedw ( usedw )

);

// 写使能,写进fifo

assign wrreq = ~full && din_vld;

// 读使能,从fifo读出来

assign rdreq = ~empty && ~busy && (usedw == 2);

assign dout = q_out;

assign dout_vld = rdreq;

endmodule

顶层

module top(

input clk,

input rst_n,

input uart_rx,

output uart_tx

);

wire [7:0] rx_data;

wire rx_data_vld;

wire busy;

wire [7:0] tx_data;

wire tx_data_vld;

// 串口接收模块

uart_rx u_uart_rx(

/* input */.clk (clk ),

/* input */.rst_n (rst_n ),

/* input */.baud_sel (0),// 波特率的选择

/* input */.din (uart_rx ),// 串口接收模块接收到主机来的1bit的数据

/* output [7:0] */.dout (rx_data ),// 串口接收模块串并转换的数据发送

/* output */.dout_vld (rx_data_vld)

);

// 串口控制模块

uart_ctrl u_uart_ctrl(

/* input */.clk (clk ),

/* input */.rst_n (rst_n ),

/* input [7:0] */.din (rx_data ),// 接收模块8位数据

/* input */.din_vld (rx_data_vld ),// 接收模块8位数据的

/* input */.busy (busy ),

/* output [7:0] */.dout (tx_data ),

/* output */.dout_vld (tx_data_vld)

);

// 串口发送模块

uart_tx u_uart_tx(

/* input */.clk (clk ),

/* input */.rst_n (rst_n ),

/* input */.baud_sel (0),// 波特率的选择

/* input [7:0] */.din (tx_data ),// 串并转换的数据

/* input */.din_vld (tx_data_vld ),// 串并转换的数据有效

/* output */.dout (uart_tx ),// 发送模块发送的1bit数据

/* output */.busy (busy ) // 发送模块忙标志

);

endmodule

串口接收发送模块同上

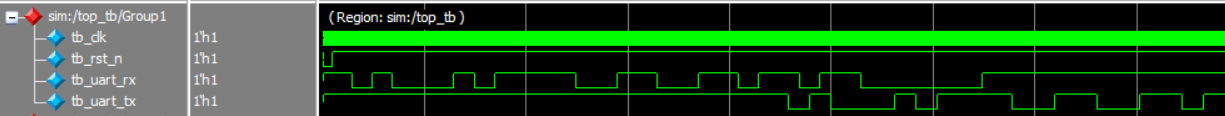

五、仿真验证

fifo就是队列,先进先出,我这里设了数据量深度为2个数据出现数据

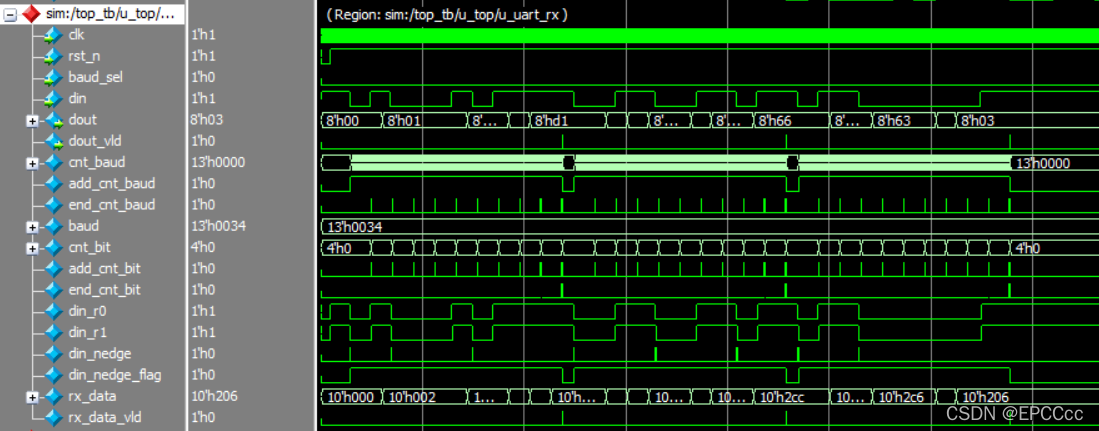

顶层仿真

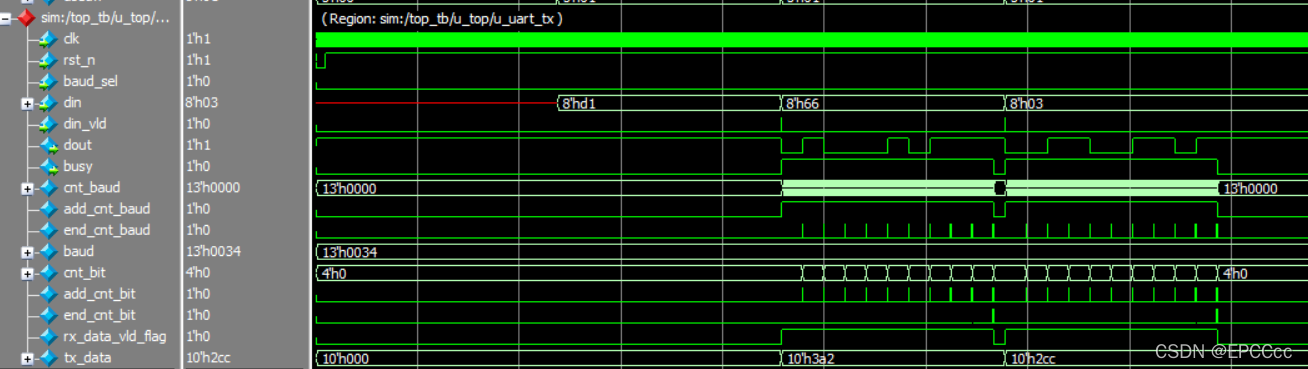

串口发送模块仿真

串口发送模块仿真

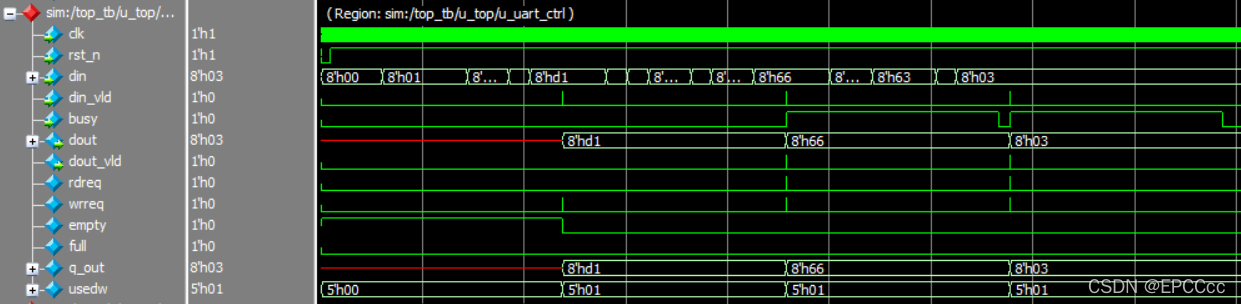

串口控制模块仿真

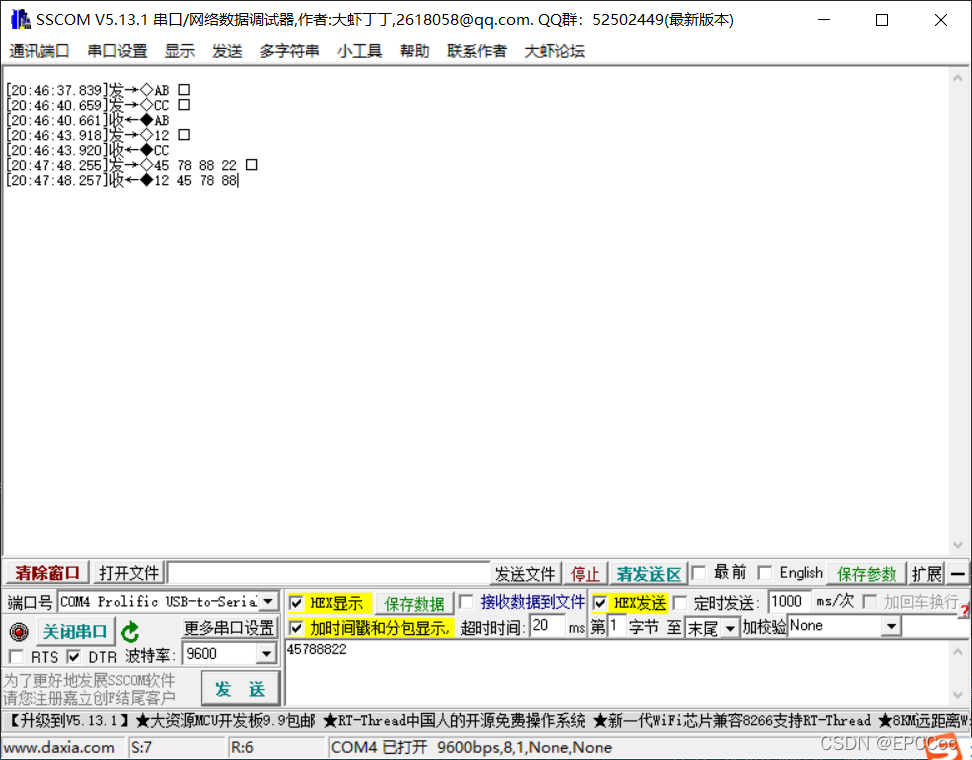

六、上板验证

七、总结

串口通信算是最最最基础的通信协议了,虽然我也当时写不出来,但是后来仔细研究,串口不难,难的是fifo。

以后再写一篇关于fifo的使用。

智能推荐

深度学习RNN-程序员宅基地

文章浏览阅读771次,点赞22次,收藏11次。只记得我在一个昏暗潮湿的地方喵喵地哭泣着。——夏目漱石《我是猫》到目前为止,我们看到的神经网络都是前馈型神经网络。(feedforward)是指网络的传播方向是单向的。具体地说,先将输入信号传给下一层(隐藏层),接收到信号的层也同样传给下一层,然后再传给下一层……像这样,信号仅在一个方向上传播。虽然前馈网络结构简单、易于理解,而且可以应用于许多任务中。不过,这种网络存在一个大问题,就是不能很好地处理时间序列数据(以下简称为“时序数据”)。

Rsync数据复制——本地数据传输_rsync本地拷贝-程序员宅基地

文章浏览阅读2.5k次。1本地数据传输类似cp的复制,实现文件,目录的增量复制。#语法模式rsync命令 参数 src源文件/目录 dest目标文件/目录1.本地文件复制# 复制hosts文件[root@chaogelinux ~]# rsync /etc/hosts /tmp/2.复制目录内容-r, --recursive 对子目录以递归模式处理# 复制/data下所有内容到/tmp[root@lb01 ~]# rsync -r /data/ /tmp/# 复制/data整个文件夹到/tmp_rsync本地拷贝

随机密码约瑟夫环_py约瑟夫环问题n,k,m要求由键盘输入值,每个人持有的密码随机生成。 2、每个函数完-程序员宅基地

文章浏览阅读1.4k次,点赞3次,收藏11次。约瑟夫环问题: 问题描述:设有编号为1,2,3……n的n个人顺时针方向围坐一圈,每人有一密码(正整数)。开始时给出一初始密码m,从编号为1的人开始报数,报m的人出列;以后将出列者的密码作为新的m,从顺时针方向紧挨着他的下一个人开始报数……直至所有人出列。试编算法,求出出列顺序。要求:用不带头结点的单向循环链表实现从键盘输入n,m各人的密码由计算机随机产生(1~10的正整数,也可以自定义_py约瑟夫环问题n,k,m要求由键盘输入值,每个人持有的密码随机生成。 2、每个函数完

[晓理紫]每日论文分享(有中文摘要,源码或项目地址)--强化学习、模仿学习、机器人_frenetix rl-程序员宅基地

文章浏览阅读1.7k次,点赞21次,收藏17次。这项研究介绍了一种自主运动规划的新方法,在Frenet坐标系内用强化学习(RL)代理通知分析算法。这种结合直接解决了自动驾驶中适应性和安全性的挑战。运动规划算法对于导航动态和复杂的场景至关重要。然而,传统方法缺乏不可预测环境所需的灵活性,而机器学习技术,特别是强化学习(RL),提供了适应性,但存在不稳定性和缺乏可解释性。我们独特的解决方案将传统运动规划算法的可预测性和稳定性与RL的动态适应性相结合,使系统能够有效地管理复杂的情况并适应不断变化的环境条件。_frenetix rl

springboot+shardingsphere实现读写分离和分库分表_spring.shardingsphere.sharding.master-slave-rules-程序员宅基地

文章浏览阅读335次。springboot整合shardingshere+druid 读写分离和分库分表,mybatis-plus_spring.shardingsphere.sharding.master-slave-rules

OSPF特殊区域NSSA配置实验(思科)_ospf naas区域实验-程序员宅基地

文章浏览阅读1.5k次,点赞2次,收藏4次。OSPF特殊区域NSSA配置实验一、实验目的二、实验内容三、实验流程四、查看和验证**OSPF特殊区域NSSA和Total NSSA配置实验总结:**一、实验目的1.掌握OSPF协议的工作原理及其LSA的类型划分;2.掌握OSPF特殊区域的概念、分类和特点;3.掌握路由器中OSPF特殊区域NSSA区域的基本配置方法和结果验证;二、实验内容完成思科路由器OSPF特殊区域NSSA区域的基本配置和结果验证;三、实验流程(一)配置任务说明如下图所示:区域0是骨干域,将区域1设置为nssa区域,完成_ospf naas区域实验

随便推点

AHAS arms调用链查询中,接口实际耗时和监听耗时差异在什么地方?_arms调用链路耗时看不懂-程序员宅基地

文章浏览阅读109次。监听耗时仅代表了 AHAS ARMS Listener(即调用链收集器)在收集并处理当前请求的调用信息时所需要的时间。它不包括网络传输、处理请求、执行操作、处理响应等其他阶段的时间,仅代表 Listener 所需的时间。通常这个时间会很短,只有几毫秒甚至更短。接口实际耗时包括了整个请求/响应周期中的所有时间,包括网络传输、处理请求、执行操作、处理响应等阶段消耗的时间。它代表了该请求在客户端发起到最终服务器响应完成所花费的总时间。_arms调用链路耗时看不懂

常见的Web应用的漏洞总结(原理、危害、防御)_web 应用中常见的漏洞及其危害有哪些-程序员宅基地

文章浏览阅读2.5k次。一、 SQL注入1.原理:SQL注入就是把SQL命令插入到Web表单然后提交到所在页面请求(查询字符串),从而达到欺骗服务器执行恶意的SQL命令。它是利用现在已有的应用程序,将SQL语句插入到数据库中执行,执行一些并非按照设计者意图的SQL语句。2.原因:根据相关技术原理,SQL注入可以分为平台层注入和代码层注入。前者由不安全的数据库配置或数据库平台的漏洞所致;后者主要是由于程序员对输入..._web 应用中常见的漏洞及其危害有哪些

离散数学——命题逻辑_离散数学命题逻辑-程序员宅基地

离散数学中的命题逻辑,包括命题的表示和联结词的运用,推理理论和常用的证明方法,如真值表法和直接证明法。还介绍了附加前提证明法或CP规则。

Spring Expression Language(SpEL)-程序员宅基地

文章浏览阅读8.6k次。Spring Expression Language(SpEL)spring的一种表达式。用来动态的获取,值、对象等。 样式: #{ …} 使用既定的规则放置在花括号中。式中的规则得以运行,可以反馈结果。理论上可以返回任何类型。 说说两种方式去设置SpELAnnotation注解。@Value()方便快捷。 你可以在里面方式任何符合SpEL规范的语句,并把它的返回值注..._spring expression language

ansible最大并发_通过这7种方法来最大程度地提高Ansible技能-程序员宅基地

文章浏览阅读1.7k次。ansible最大并发 Ansible是一种功能强大的无代理(但易于使用且轻巧)的自动化工具,自2012年推出以来一直稳步流行。这种流行在一定程度上是由于其简单性。 默认情况下,Ansible的最基本依赖项(Python和SSH)几乎在所有地方都可用,这使得Ansible可以轻松用于各种系统:服务器,工作站,Raspberry Pi,工业控制器,Linux容器,网络设备等。 Ansible可..._ansible 提升 高并发

Barcode Reader在45毫秒内实现条码识别-程序员宅基地

文章浏览阅读479次。应我的客户要求,需要找到一款可以在极短时间识别二维条码的软件以应对他们现在极其迅速的货品入库需求。正好听说过一款Dynamsoft Barcode Reader的开发包,根据其官网介绍最新版对条码检测速度比以前的版本快2倍以上。根据对Dynamsoft Barcode Reader8.8SDK包拆解,其中含了JavaScript Package /.NET Package /C/C++ Package /Python Package /Java Package /iOS Package /A..._barcode reader